figure \cftpagenumbersofftable

Tuning of Nuclear Spectroscopic Telescope Array (NuSTAR) Application Specific Integrated Circuits (ASICs) to improve low energy threshold of future Hard X-ray Imaging Detectors

Abstract

Detector commanding, processing and readout of spaceborne instrumentation is often accomplished with Application Specific Integrated Circuits (ASICs). The ASIC designed for the Nuclear Spectroscopic Telescope Array (NuSTAR) mission (NuASIC) enables future tiled CdZnTe (CZT) detector array readout for x-ray detectors such as the High Resolution Energetic X-ray Imager (HREXI). Modified NuASIC gain settings have been implemented for HREXI’s broader targeted imaging energy range (3-300 keV) compared to NuSTAR (2-79 keV), which may require updated NuASIC internal parameters for optimal energy resolution. To reach HREXI’s targeted low energy threshold, we have also enabled the NuASIC’s “Charge Pump Mode” (CPM), which introduces an additional tuning parameter. In this paper, we describe the mechanics of the NuASIC’s adjustable parameters and use our recently developed ASIC Test Stand (ATS) to probe a “bare” NuASIC using its internal test pulser. We record the effects of parameter tuning on the device’s electronics noise and low energy threshold and report the optimal set of parameters for HREXI’s updated gain setting. We detail a semi-automated procedure to derive the optimal parameters for each of HREXI’s large area, closely tiled NuASIC/CZT detectors to expedite instrument integration.

keywords:

ASIC, NuASIC, X-ray, CdZnTe detectors⋆[email protected]

†NASA FINESST Fellow

1 Introduction & Motivation

Time-domain and multi-messenger astrophysics are priority science objectives for astronomy over the next decade[1] and will illuminate the most extreme astrophysical processes. To contribute to this discovery regime, we are developing a large area closely tiled CdZnTe (CZT) imaging detector, the High Resolution Energetic X-ray Imager (HREXI). HREXI is the detector for a wide-field coded aperture telescope, the HREXI SmallSat Extremes Explorer (HSEE), currently in formulation (Grindlay et al. 2023)[2]. The HSEE telescope enables broad-band (3-300 keV) imaging with high spatial and spectral resolution to enable pioneering new studies of long and short Gamma-Ray Bursts (GRB), blazar flares, outbursts from magnetars, super-luminal supernovae, tidal disruption events and low-level x-ray flares from black hole low mass x-ray binaries to measure their poorly understood population and formation. The broad-band imaging of HSEE will extend detections and sharpen locations of short x-ray/gamma-ray bursts coincident with gravitational wave detections from merging neutron star (or neutron star–black hole) binaries. Broad-band spectra and 40 arcsec locations of high redshift long GRBs will allow us to trace the epoch of formation of the very first (Pop III) stars[3].

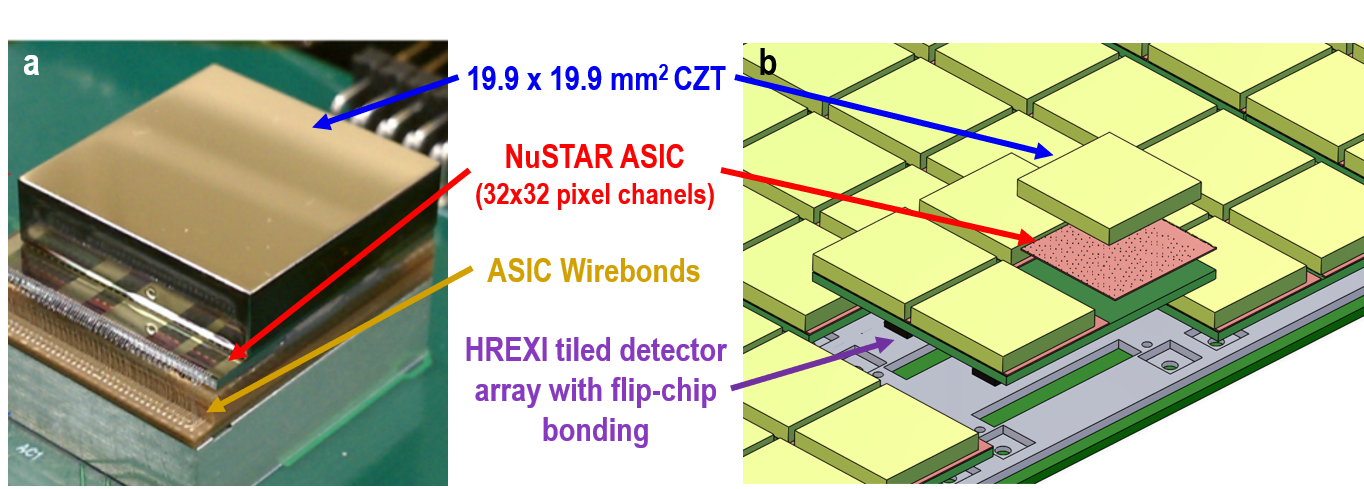

HSEE draws on technology studied for large area CZT arrays for the EXIST telescope proposed for Astro2010[4] and initially developed with the ProtoEXIST 1 & 2 balloon-borne x-ray telescope experiments[5, 6, 7, 8, 9]. The HSEE detector plane will be composed of a closely tiled array of 19.9 19.9 mm2, 3 mm thick pixelated CZT detectors, each read out by an Application Specific Integrated Circuit (ASIC) originally developed[10, 11, 12] for the Nuclear Spectroscopic Telescope Array (NuSTAR) mission[13]. The electrical connection of each of the individual CZT pixels (0.55 0.55 mm2 pixel active area) to the system for readout is completed with conductive-epoxy bonds to gold studs attached to a matching pattern of input pads (32 32 pads, 0.6 mm pitch) on the upper surface of the NuSTAR ASIC (NuASIC). The full HSEE detector plane will consist of a 16 16 detector array (960 cm2) compatible with the effective area and sensitivity requirements of a coded aperture telescope. An example of a single CZT detector produced for the ProtoEXIST2 detector plane is shown in Figure 1a and a model of the tiled array of such detectors to realize the HSEE detector plane is given in Figure 1b.

The operational parameters of the NuASIC (e.g., threshold, gain select, etc.) are controlled with a single user-programmable command register that enables the adjustment of 15 separate parameters, as well as an enable bit for each of the 1024 pixels and control of the internal test-pulse routing. The optimization of a NuASIC’s resolution and low energy threshold is accomplished in this work through adjustment of a set of these on-board parameters. While optimal settings were determined manually for NuSTAR’s two telescopes, each with 2 2 CZT/ASIC detectors, HSEE’s larger 256 detector array will require systematic and automated parameter selection for each CZT/ASIC for time- and cost-saving during instrument integration.

HSEE’s science objectives require sensitivity over a broader range of energies (3-300 keV) than NuSTAR (2-79 keV). NuASICs flown on HSEE will operate with slightly reduced signal gains in order to achieve this expanded dynamic energy range; 4 different global preamplifier gain settings are selectable through a 2-bit gain select register (gainsel). Fundamentally, the gainsel setting modifies the feedback capacitance value of the NuASIC pixel’s charge sensitive preamplifier. As the feedback capacitance is increased the preamplifier output current is conversely reduced. This allows for a broader range of photon energies before saturating the NuASIC’s 12-bit analog-to-digital converter (ADC). To achieve the desired dynamic pixel energy range of up to 350 keV, the HSEE detectors will operate with a gainsel setting of 1, compared to the highest gain setting used on NuSTAR, gainsel = 0. In this paper, we evaluate how our modified NuASIC gain setting will affect the optimal set of NuASIC internal parameters and explore device optimization to achieve the best resolution and low energy threshold.

We explore the sensitivity of the NuASIC to these internal parameter adjustments in a normal operating configuration as compared to a “Charge Pump Mode” (CPM) that further reduces the standing current at the preamplifier output which, in turn, suppresses detector noise and improves energy resolution. For this study, we have tested a Through-Silicon Via (TSV) enabled NuASIC (described by Hong et al. 2021)[14] that has been modified to have the 87 commanding, power, and readout lines routed through the NuASIC’s silicon substrate to its back surface through a via-last process[15]. This TSV-enabled design will ultimately improve instrument integration by replacing the previously required 87 individual wire bonds per detector with a simpler and more robust flip-chip bonding process. To probe a “bare” unattached TSV-NuASIC we have designed and built an ASIC Test Stand (ATS) for control and data readout that contacts the device using an array of micro-pogo probes[16, 17]. We utilize the NuASIC’s internal test pulser to simulate fixed-energy x-ray events in each pixel channel and to determine the impact of NuASIC parameter adjustments.

We next provide an overview of the operation of the NuASIC in order to clarify how x-ray events are captured and recorded. This includes a description of the five tuning parameters that may be adjusted within the NuASIC to aid in stabilizing operation and achieving optimal energy resolution and low energy threshold. We then provide a summary of the results obtained from operating the NuASIC in normal mode and CPM through pixel channel analog output and the NuASIC’s digital readout. Lastly, we discuss the effect of choosing the optimal parameter set for the NuASIC in both normal mode and CPM, and how these different operational modes will impact the detector’s resolution and low energy threshold.

2 NuASIC Parameter Overview

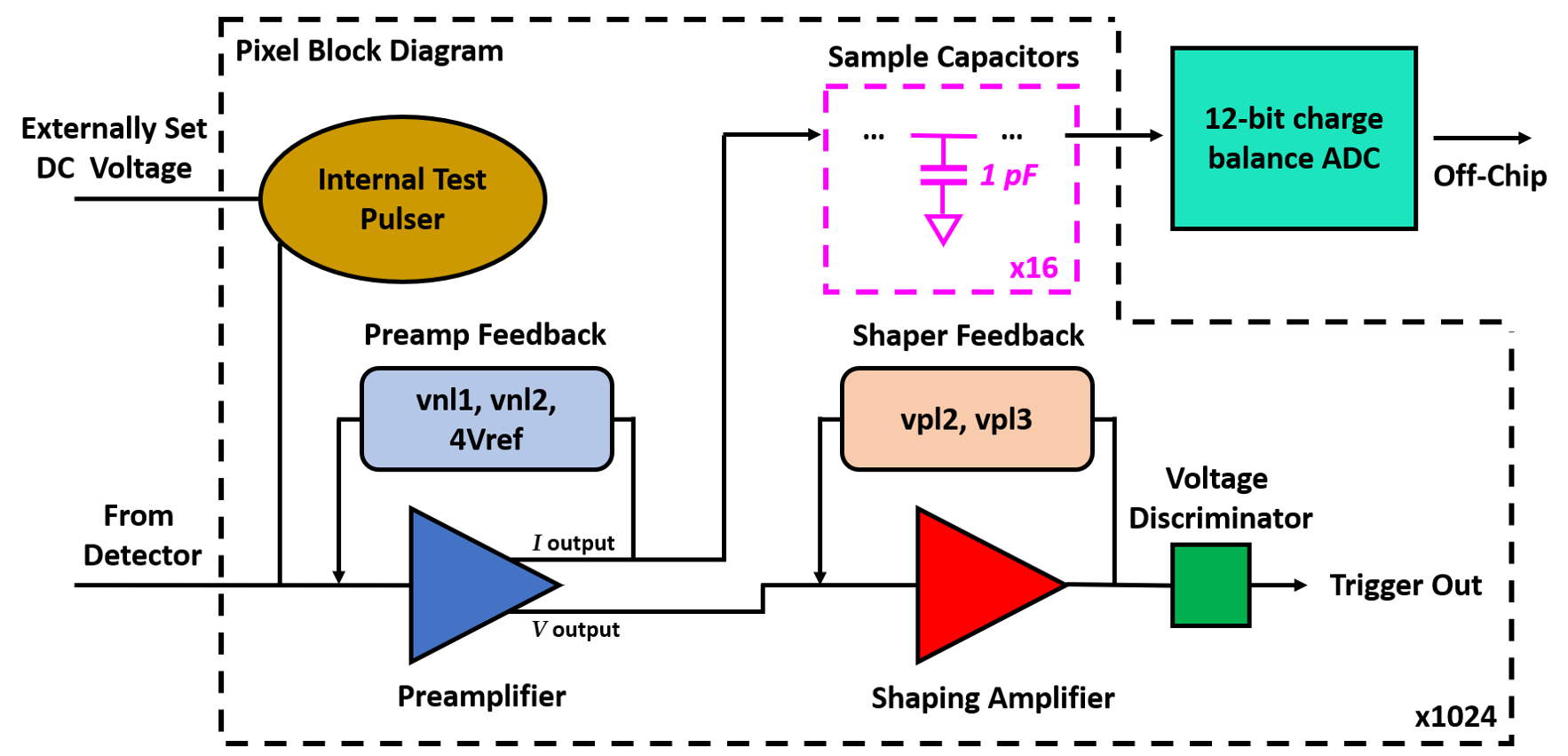

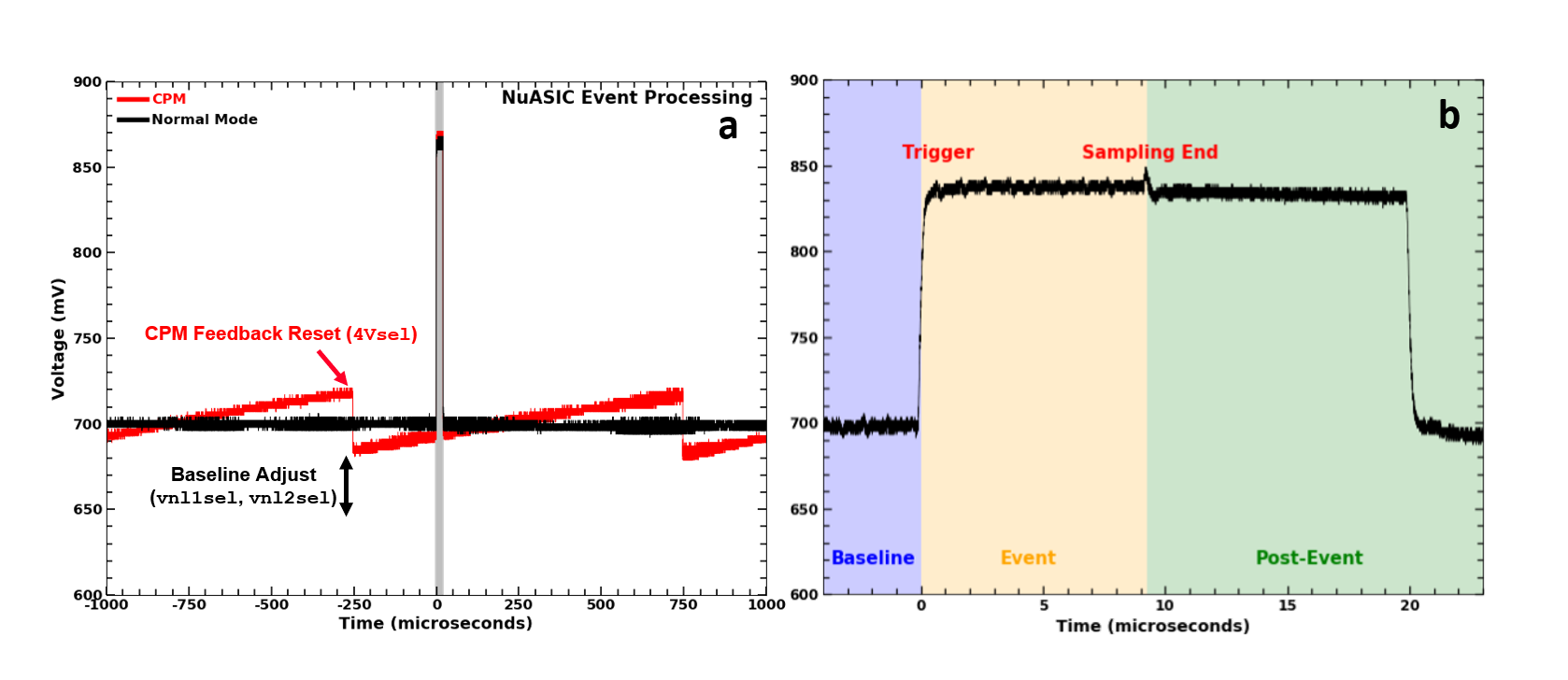

To understand the tunable parameters of the NuASIC, we first explain the device’s basic operation. When any of the NuASIC’s 1024 pixel channels receives charge from a photon event or an internally driven test pulser, a series of steps allows for the capture of the signal which can be seen in Figure 2. The event charge is received by the pixel preamplifier and produces a voltage and current output. The voltage output is routed through a shaping amplifier to a voltage discriminator. If the signal surpasses the required programmable threshold, a trigger will be sent off-chip to an external controller (a Complex Programmable Logic Device, CPLD) to begin the NuASIC’s event processing. Before an event is triggered, baseline charge from the preamplifier is sequentially collected on a bank of 16 capacitors with a 1 s cadence driven by a sampling clock. When a triggering signal arrives, the sampling clock runs for eight additional cycles to capture the event’s charge before stopping. When the capacitor bank’s charge is then sampled through the NuASIC’s 12-bit charge-balance ADC, it contains eight pre-event baseline charge samples and eight charge samples from the event before being returned to a baseline voltage level. The captured baseline and event data are then transmitted off-chip where the baseline values are subtracted from the signal values to determine the energy of the event. A duplicate current output is returned to the preamplifier input in a feedback loop, which has its resistance set by a smaller value resistor, a current divider sequence, and an amplifier[10]. This feed back loop balances out pixel leakage current and generates the standing current baseline, which is the DC current at the amplifier input or output when no signal from the attach detector or internal pulser is received. After a 1.8 ms post-trigger processing delay (for a single event reading out a 3 3 pixel patch), the NuASIC then returns to an ”armed” state until triggered by the next x-ray event. For a more detailed description of the fundamentals underlying the NuASIC design and operation, see Cook et al. 1998.[10]

The NuASIC supports a single output line which may be commanded to output the preamplifier and shaping amplifier signals for any of the individual pixels. We use this output as an additional diagnostic tool which enables us to directly observe the pixel-by-pixel changes to these outputs which can be compared to shifts in the sampling capacitor’s baseline voltage level though the NuASIC’s 12-bitcharge-rebalance ADC readout as a function of our parameter adjustments. Figure 3a shows an example of the oscilloscope-captured traces of this preamplifier analog output readout with 3b providing a zoomed-in view of the process. With the exception of the individual pixel enable and test pulser enable masks, the adjustable parameters of the NuASIC are global, and applied simultaneously to all pixels. The standing current at the preamplifier input is increased by the vnl1 bias current, which is used to balance pixel leakage current, and the vnl2 bias current which adjusts the pixel sampling current. Both of these settings are controlled with bias voltage adjustments modified by electronically changing a bank of analog switches via two 2-bit settings (vnl1sel and vnl2sel respectively) in the NuASIC’s command register. Vnl1sel can be adjusted over a 40 mV range while vnl2sel modifies the vnl2 bias current as a fraction of the vnl1 bias current. Modifying these global pixel preamplifier settings allows us to counteract pixel input leakage current while minimizing the standing current at the preamplifier output. By minimizing the standing current passing through the preamplifier, the NuASIC reduces shot noise in the signal readout, which manifests as rms current that scales as a square root of the standing, or DC baseline current, and which would result in larger variance in the sampling capacitor bank charge. The best set of the vnl1sel and vnl2sel parameters will result in the lowest preamplifier standing current while still maintaining stable NuASIC readout. However, since the settings are applied globally the optimal parameters are a compromise between the performances of all of the individual 1024 pixels. The vnl1sel and vnl2sel parameters are summarized in Table 1 alongside the three remaining global NuASIC parameters described below.

The shaping amplifier bias current is modified by adjusting the vpl2 and vpl3 bias currents, which in turn adjusts the amplifier pulse height and settling time. These bias currents are adjusted by changing the vpl2 and vpl3 bias voltages over a 375 mV range with commandable onboard 4-bit digital-to-analog converters (DACs) (vpl2sel and vpl3sel) respectively. It is important for the shaping amplifier signal level to be linear with respect to input voltage and have a fast settling time, as otherwise the discriminator trigger threshold also becomes non-linear. Non-linearity hinders the choice of a global discriminator value that accurately sets the desired energy threshold. The best set of shaping amplifier command register settings – and therefore discriminator linearity – is thermally sensitive, and at lower temperatures (0∘ C), modified vpl2sel and vpl3sel values will most likely be used.

The NuASIC may additionally be run in CPM which reduces signal noise in exchange for enhanced sensitivity to leakage current. We anticipate that operating with 3 mm thick CZT produced by Redlen Technologies and a -400V bias will result in a predicted 10-20 nA of leakage current through the ASIC, which meets CPM’s leakage current requirement (200 pA vs 400 pA maximum per pixel) under the assumption of uniform leakage current. Normal mode operation returns feedback current (a fraction of the output) directly to the preamplifier input. CPM instead uses a charge injection circuit to return 1/20th of the normal mode feedback current to reduce standing current at the preamplifier input (and shot noise in the readout) while still maintaining leakage current balancing. This reduction in feedback current is performed with a capacitive divider circuit that must be periodically (1 kHz frequency) reset from a voltage reference (by disconnecting from the preamplifier input and connecting to the reference) intended to match the preamplifier input voltage. This circuit must be periodically reset or the preamplifier feedback cannot correctly balance input charge and the preamplifier baseline begins to diverge. The switching action to maintain the capacitive divider circuit causes small DC bias fluctuations at the preamplifier input which manifest as voltage ramping on the amplifier output. This 4V (actually a range of 3.92V to 4.02V) reference can have its voltage modified to reduce the DC bias fluctuations by commanding a 7-bit on-chip DAC with the 4Vsel settings from the command register. This baseline voltage ramping and reset pattern can be seen in CPM’s example preamplifier analog output in Figure 3a. The slope of this voltage ramping trends across the NuASIC, likely as a function of pixel distance from the NuASIC ADC and readout time. While these perturbations therefore cannot be nulled entirely as any local optimization with 4Vsel will negatively affect non-adjacent pixels, they can still be minimized.

In this work, we describe the effect of tuning the five NuASIC parameter registers listed in Table 1 for operation in both normal mode and CPM. We compare our results against optimal values derived for the NuSTAR mission’s gain settings. In order of operation, the vnl1sel and vnl2sel parameters are modified together to adjust the preamplifier baseline. The combination of these 2-bit registers results in 16 potential preamplifier operation states. vpl2sel and vpl3sel are 4-bit registers that adjust the shaping amplifier vpl2 and vpl3 bias voltages respectively and modify the voltage profile passed to the event trigger discriminator. While operating in CPM, minimization of the preamplifier output voltage ramping is performed with the 7-bit 4Vsel register by choosing a global voltage setting that minimizes DC bias fluctuations at the preamplifier input for the majority of NuASIC pixels.

3 Results of Normal Mode and CPM Testing

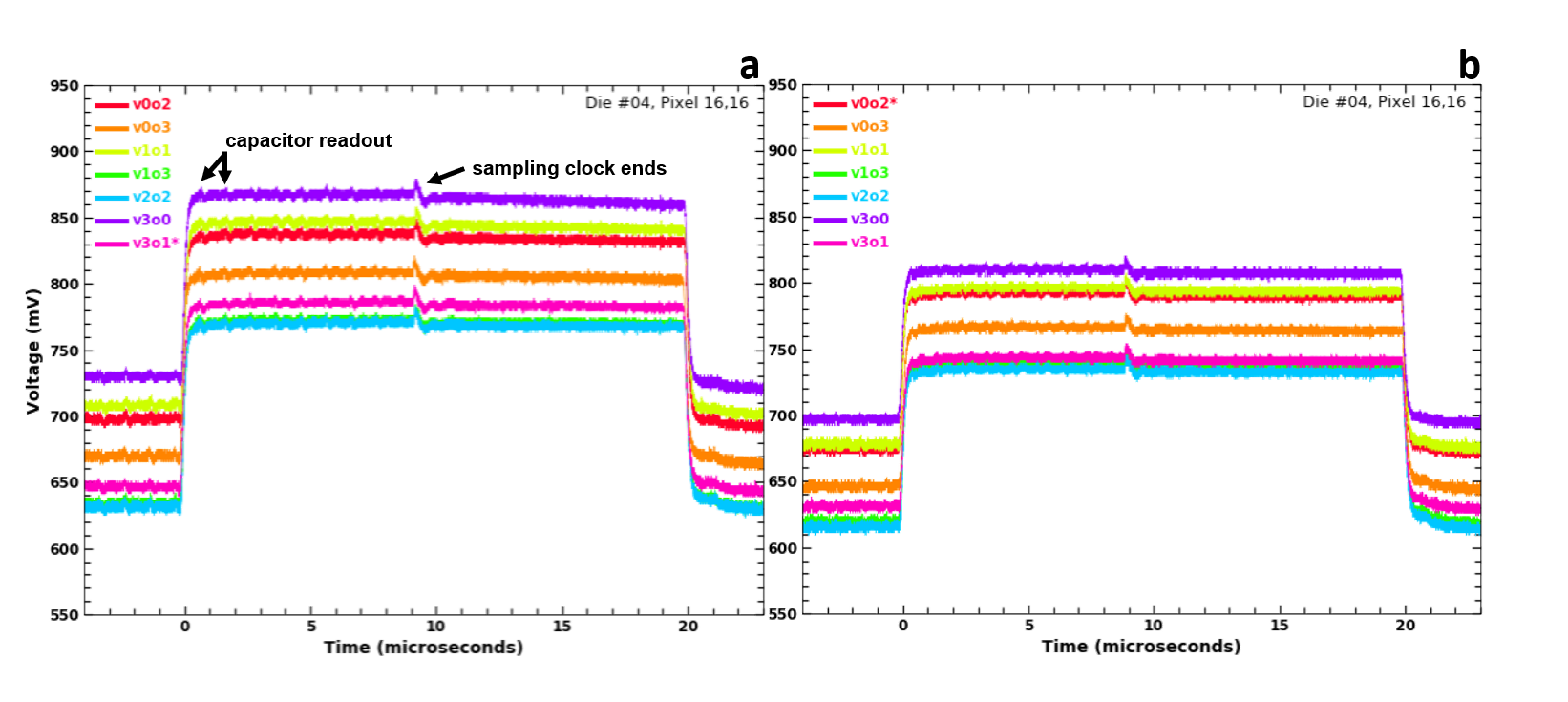

Analog outputs from the preamplifier under normal mode and CPM conditions were first collected with an oscilloscope and are shown in Figure 4. During testing, the vnl1sel and vnl2sel parameters were modified, which resulted in a shift in the preamplifier voltage baseline from approximately 630 mV to 730 mV in normal mode, shifting the floor of the signal without modifying the pulse height. Figure 4a includes preamplifier traces from normal mode while Figure 4b are from CPM with identical vnl1sel and vnl2sel settings, but resulting in slightly different baseline values. Before a signal is triggered, the sampling clock is continuously running on the baseline and can be seen as periodic 1 s perturbations on the signal. These perturbations continue for 8 s after the event trigger as the signal energy is recorded onto the final eight sampling capacitors. After readout this ultimately allows for a calculation of event energy by subtracting the signal from the baseline. The baseline value from the 12-bit ADC readout shifts from 524 analog-to-digital units (ADUs) to 1044 ADUs over the 630 to 730 mV range. A full record of analog baseline values for the tested parameters are listed in Table 2 alongside keywords for their associated vnl1sel and vnl2sel register value combinations. At 9 s after the event trigger, the sampling clock stops and the NuASIC enters into a locked post-trigger phase before readout. In both normal mode and CPM, vnl1sel and vnl2sel setting combinations that resulted in baselines lower than those shown in Figure 4 produced fluctuating baseline levels. These fluctuating baselines generated noise triggers and lowered detector performance by reducing signal resolution and generating additional “dead time” as pixel readout time increased. CPM is overall less affected by the baseline change due to the modified feedback network, and a baseline value can be chosen to approximately match the normal mode value (v0o2, the value used by NuSTAR, or v0o3).

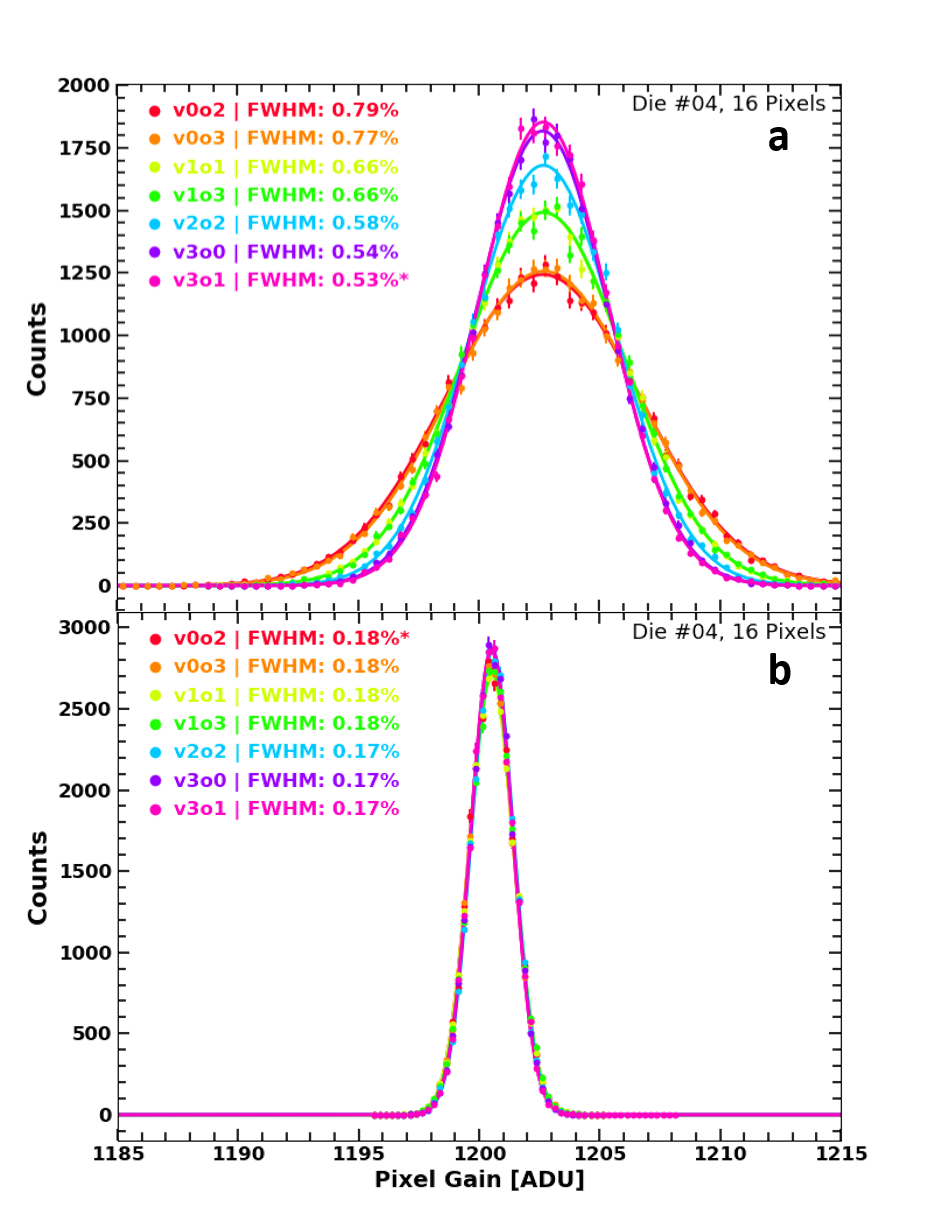

The results of modifying the preamplifier vnl1sel and vnl2sel parameters and adjusting the baseline can be observed in Figure 5. We tested a patch of 16 pixels with the NuASIC’s internal test pulser with various combinations of preamplifier register settings. Each pixel’s gain was calibrated and the resolution of the patch was calculated from the distribution of event energies and compared across different combinations of register settings. In Figure 5a, normal mode resolution is directly improved by reducing the standing current baseline of the preamplifier. The best results are achieved at NuSTAR’s normal mode default register values of vnl1sel 3 and vnl2sel 1 (v3o1) with a 0.53% Full Width at Half Maximum (FWHM) resolution. The parameter with the most noticeable effect on pixel resolution is vnl1sel, with each register step increase improving resolution by 0.1% FWHM. The vnl2sel parameter, while contributing to baseline shifts in Figure 4, has a less noticeable effect on the pixel channel resolution. In Figure 5b, CPM demonstrates an improved resolution of 0.18% FWHM at the mode’s default settings (v0o2). While operating in CPM, there was no significant resolution change from modifying vnl1sel and vnl2sel. This is most likely because the CPM feedback mechanism returns only a fraction (1/20th) of the standing current at the preamplifier output.

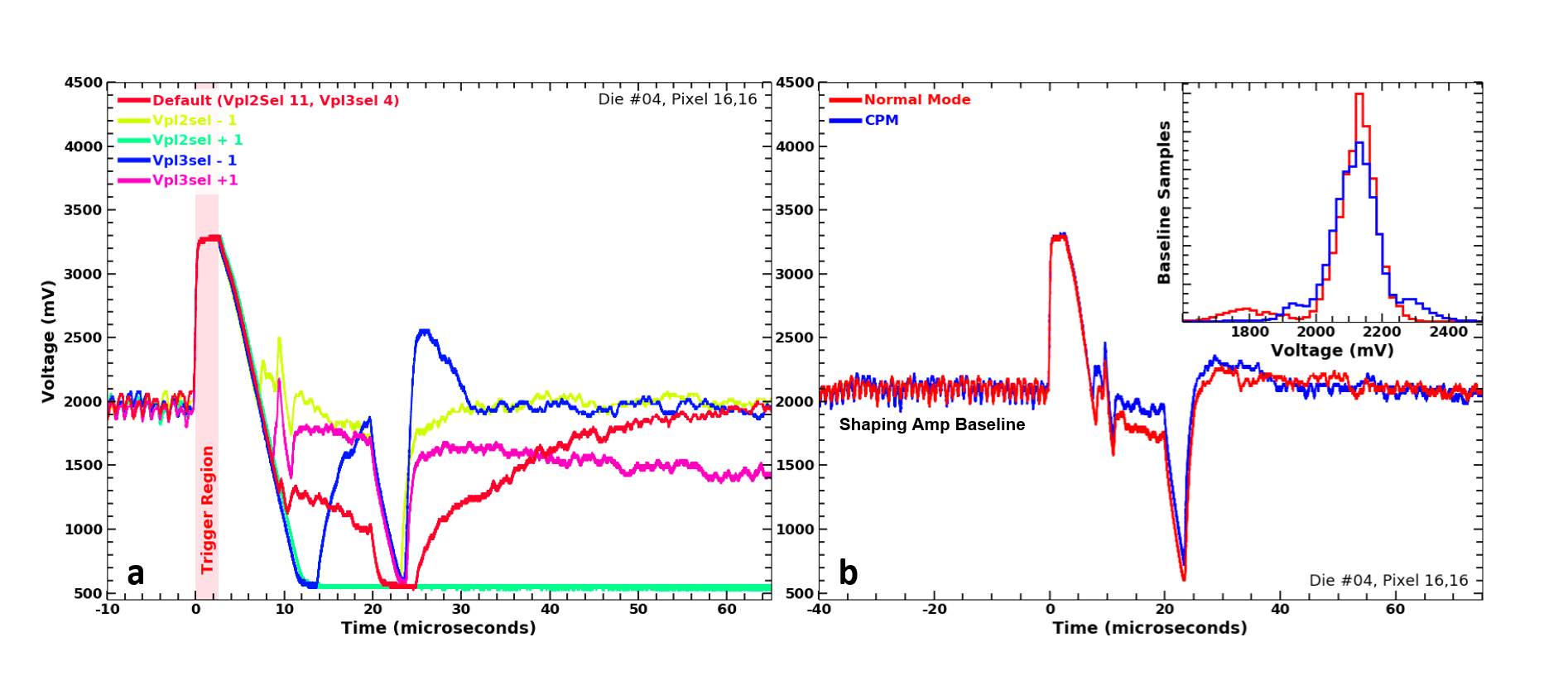

We also explored a selection of shaping amplifier bias voltages for the NuASIC with command register settings listed in Table 3. By modifying the bias voltages with vpl2sel and vpl3sel, a variety of shaping amplifier profiles can be obtained. Records of oscilloscope-captured analog output traces from the shaping amplifier can be seen in Figure 6. The pulse height of the signal is important as the discriminator will latch the NuASIC depending on its amplitude and corresponding discriminator value. The shaping amplifier should ultimately be adjusted to have a linear response to changing signal strength, while quickly returning to a stable baseline value. Adjustments to vpl2sel and vpl3sel primarily modify the height and duration of the primary peak and the duration of time before the signal is returned to the baseline, and are shown in Figure 6a. The default register settings of vpl2sel = 11 and vpl3sel = 4 (3.850V and 4.475V, respectively) were tested by NuSTAR to yield a linear response across the discriminator energy range. Future work will explore the effect of modifying the shaping amplifier parameters under different thermal conditions we may expect during a HREXI flight mission. We compared analog output traces from the shaping amplifier in both normal mode and CPM, which is shown in Figure 6b. We expected that while operating in CPM the shaping amplifier baseline before the signal would be less noisy and would allow for easier separation of weak signals from the background. This reduction in baseline shaping amplifier noise was not observed. We note that without the attachment of a detector under bias, that CPM does not further improve the low energy threshold, however further testing will be required to make this determination for actual detectors systems and will be carried out in subsequent work.

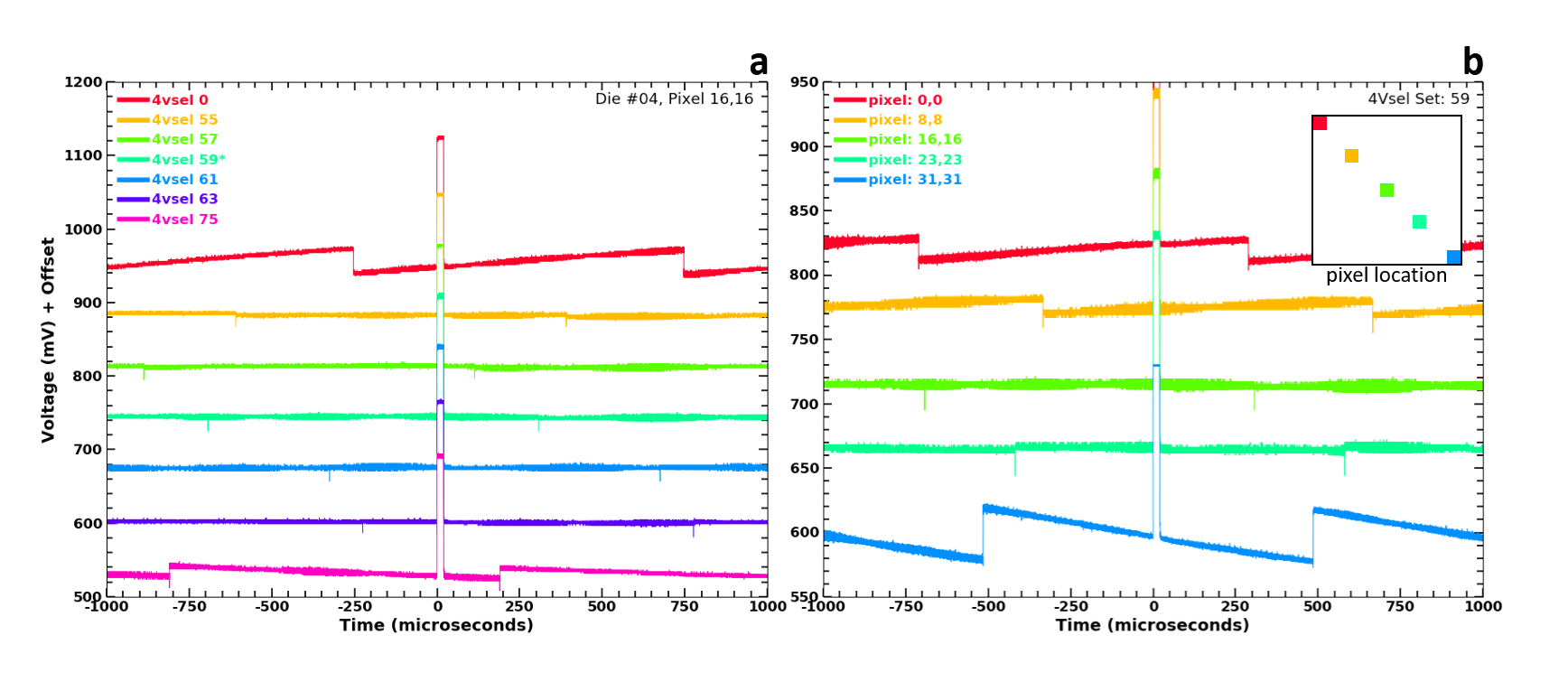

In addition to these four tuning parameters that can be explored in the NuASIC’s normal mode operation, CPM introduces a feedback charge reset voltage level that can be modified by the 4Vsel register to precisely adjust an internal 4V reference. The impact of the CPM feedback reset appears as voltage ramping in the preamplifier outputs, and can trend both positively and negatively as can be seen in Figure 7. This figure is a longer time-scale snapshot of the analog preamplifier output that is shown in Figure 4, with the pulser event signal located at the center of the oscilloscope trace. In Figure 7a, a NuASIC pixel’s oscilloscope trace is shown while operating in CPM with various 4Vsel register settings. As the 4Vsel register value changes from 0 to 75, the magnitude and slope of the voltage ramping effect changes, with optimal “flat” readout occurring between register values of 56 to 61 (4V reference voltages of 3.975 and 3.972, respectively). 4Vsel register values greater than 75 had a tendency in the current firmware version to cause reset-induced fake event triggers due to the large positive edge of the reset signal. This will be corrected in the next firmware update, although 4Vsel register values greater than 75 will not be typically used. Figure 7b demonstrates how the preamplifier baseline voltage ramping effect is not flat across the device and trends from pixel (0,0) to (31,31) by sampling analog preamplifier traces from several pixel locations across the device. This trending still exists after minimizing the ramping effect on the central pixels. Although the ensemble of 1024 NuASIC pixel baseline slopes are minimized for this device at a 4Vsel value of 59, the effect of this voltage ramping will need to be accounted for in pixels at the edges of each NuASIC.

4 Discussion of Optimal Register Settings

Under both normal mode and CPM operation, the preamplifier vnl1sel and vnl2sel parameter settings confirmed that the NuSTAR default values (normal mode: v3o0; CPM: v0o2) continue to be optimal for HREXI’s chosen gain setting and larger full-scale energy range. In normal mode, attempting to use register settings that result in a lower baseline (vnl1sel = 0, vnl2sel = 0/1) typically caused unstable NuASIC operation. As a result, fluctuations that appear in the baseline generate a large number of false triggers, increasing the detector’s “dead time”. Similar effects were observed while operating in CPM, with both the lowest baselines and highest baselines (vnl1sel = 3, vnl2sel =3) becoming unstable. Optimal register values for the shaping amplifier have also not changed, with register values of vpl2sel and vpl3sel of 11 and 4 respectively for room temperature testing. Further exploration of these values with a bonded CZT detector will be carried out in future work in our Thermal Vacuum Chamber (TVAC). This will enable us to repeat these experiments and confirm the linearity of the shaping amplifier output under realistic flight-like conditions at lower operating temperatures.

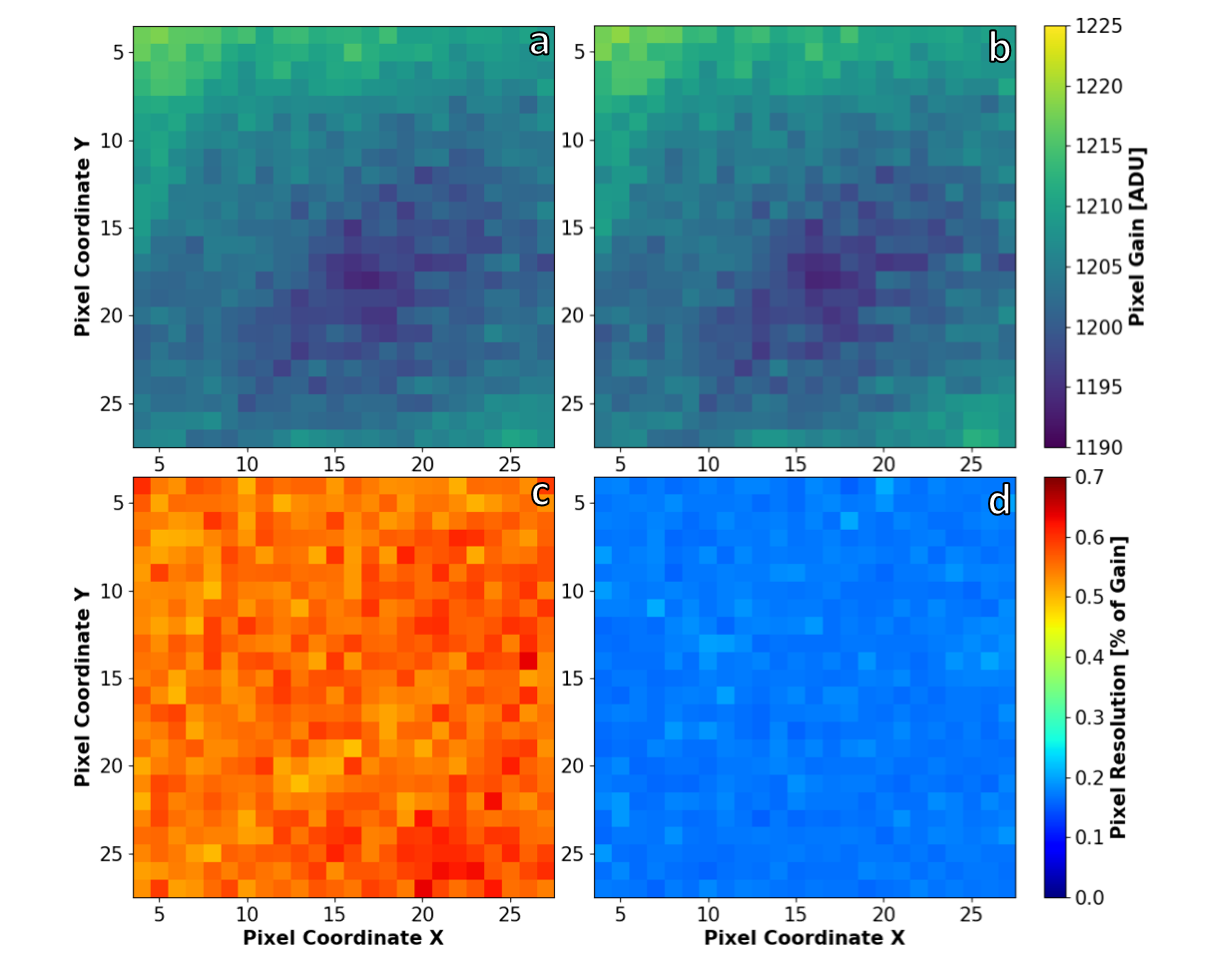

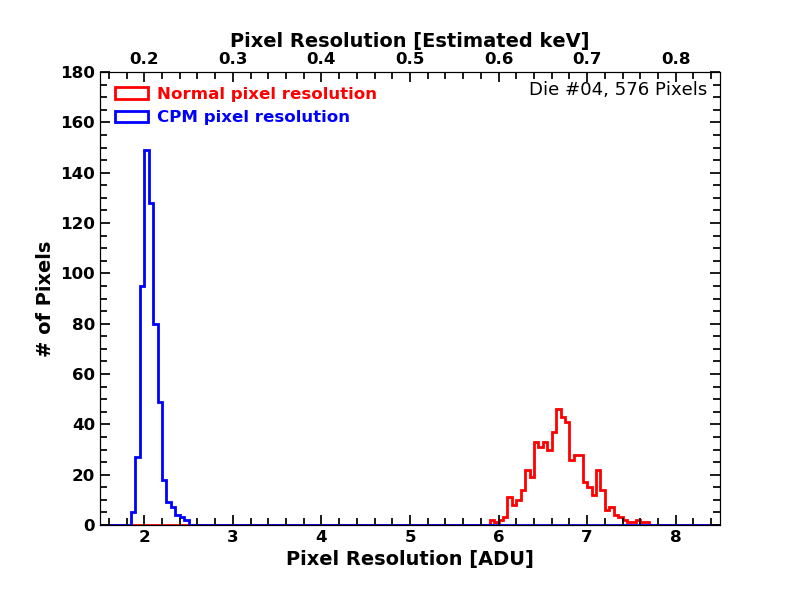

Enabling CPM with a optimally selected 4Vsel parameter results in a 3-fold improvement in pixel channel resolution on a “bare” NuASIC. The mean pixel channel resolution improved from 6.7 ± 0.3 ADU (0.7 keV) under optimal normal mode settings to 2.1 ± 0.1 ADU (0.2 keV) when operating in CPM. The resolution and gain performance of the central 576 (24 24) pixels of the NuASIC can be seen in Figure 8. This NuASIC pixel resolution and gain map was acquired by activating the NuASIC pixels’ internal test pulsers in 4 4 patches and recording the mean and variance of the pulser event energy output. The 4 4 pulser patch was stepped across the NuASIC until all of the central 576 pixels were scanned, while noise-generating edge pixels external to the region under test were disabled via a commandable pixel mask. Figures 8a and 8c include the gain and resolution data while the NuASIC operates in normal mode while 8b and 8d similarly include the pixel gain and resolution data of CPM. Across the NuASIC, pixel resolution improves by a factor of 3 while pixel gain remains nearly identical, with uncalibrated pixel gain median values shifting no more than ± 3 ADU. The uneven pixel gain pattern across the NuASIC is due to the inherent variance in properties of the independent pixel channel preamplifiers and routing paths to the NuASIC 12-bit ADC. The pixel gain pattern ultimately is calibrated, resulting in the pixel resolution results shown (Figure 8). A histogram containing the resolution data of all pixels scanned in the pixel map is shown in Figure 9. The binned pixel data demonstrate that CPM improves the median NuASIC pixel resolution, as well as improves the resolution uniformity across the pixels.

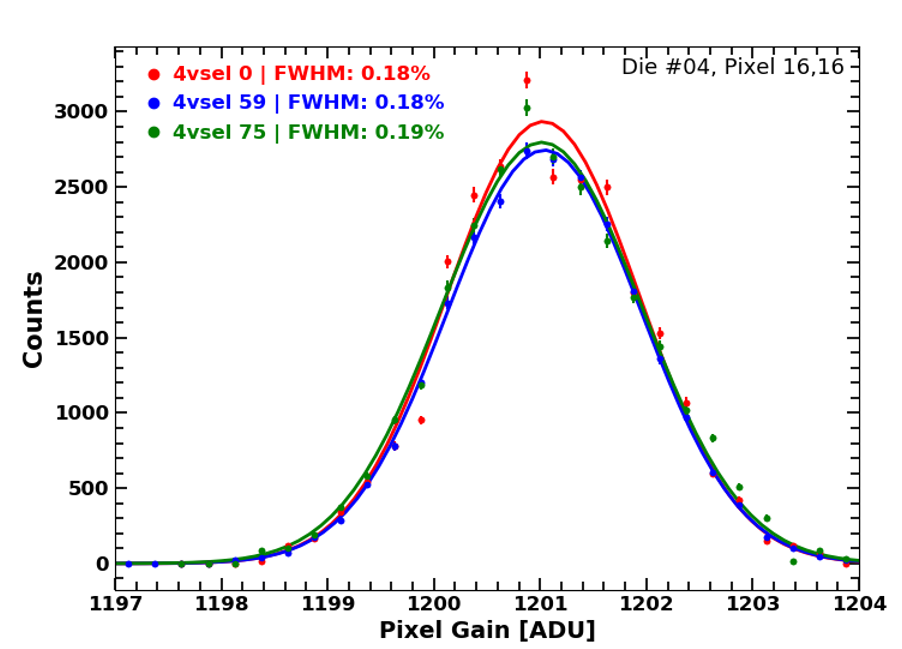

This improvement in resolution will ultimately be affected by the optimally chosen 4Vsel register value. Figure 10 includes resolution data from the pixel (16,16) data presented in Figure 7a for the most optimal 4Vsel value of 59, as well as values with strong positive and negative voltage ramping (4Vsel of 0 and 75, respectively). While testing on the ATS results in little resolution degradation for this pixel at sub-optimal 4Vsel selections, the impact is expected to be much greater after bonding to a CZT detector and while operating under a high voltage bias. The additional leakage current and greater pixel readout rates (affecting CPM reset timing) are expected to induce additional noise in the detector, for which this 4Vsel optimization will be important.

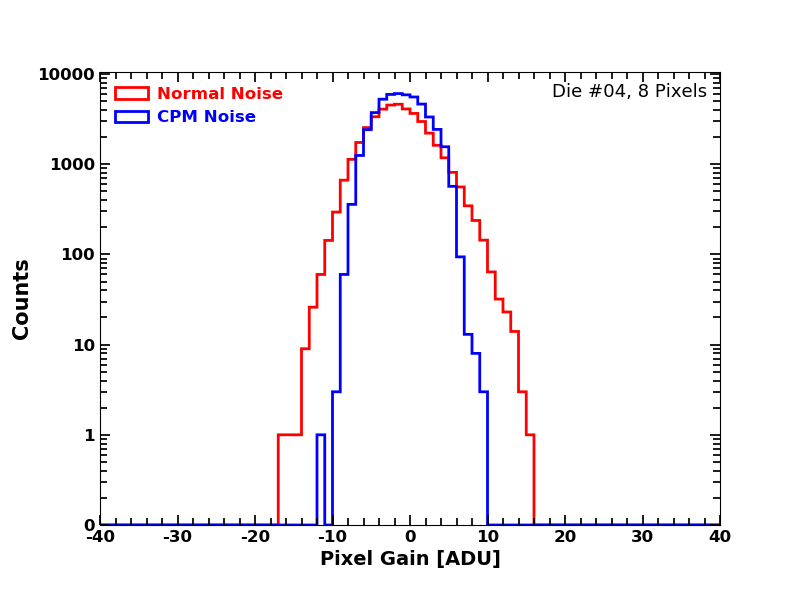

Measurements of the noise distribution are performed for both optimal normal mode and CPM data. When a pixel trigger is detected on the NuASIC, we command a 3 3 pixel patch readout, allowing the sampling of pixels adjacent to the triggered pixel that have no injected charge. The distribution of these noise-only samples is shown in Figure 11. We collected noise distribution data from tests performed at both a high discriminator threshold (20 keV) and a low threshold (3.5 keV). A 6 ADU reduction in noise distribution spread is observed when moving from normal mode operation to CPM while operating at a low discriminator setting (3.5 keV). The noise distribution directly affects the low energy threshold of NuASIC readout, as an ADU value of 20 corresponds to the lowest NuASIC discriminator setting at 2 keV. While the ATS is operating the NuASIC without an attached detector and the noise distribution is expected to be broader under normal detector conditions, the testing performed on the ATS confirms that operating in CPM will improve (i.e., lower) the NuASIC’s low energy threshold due to electronic noise. With an attached CZT crystal, we expect our detector’s noise distribution to be broader due to leakage current. In turn, we may see a larger factor of noise distribution reduction while operating in CPM which will be explored in future work.

5 Summary and Future Development

From our NuASIC testing and discussions with the NuSTAR team, we have determined that the default parameters prescribed for the NuASIC and flown on NuSTAR are expected to still work optimally for the modified gain settings required for the broader HREXI energy band. In our planned CPM operation, this will result in default parameter settings of vnl1sel = 0 and vnl2sel = 3 to set the preamplifier baseline voltage to 680 mV. The shaping amplifier’s optimal settings will also remain as the defaults at vpl2sel = 11 and vpl3sel = 4. NuSTAR updated these optimal settings to as low as vpl2sel = 9 and vpl3sel = 4 in cooler operating temperatures (0∘ C), and we also expect to modify these settings according to the detector’s flight conditions. The optimal range of 4Vsel values for flattening preamplifier voltage ramping while operating in CPM appears to range between register values of 50 and 65, which will need to be fine-tuned for each NuASIC in the HREXI detector readout. However, by digitizing the CPM reset phase information and minimizing the voltage ramping slope in parallel for all pixels across the device with the 4Vsel command register, we will be able to semi-automatically perform this correction.

Fabrication, testing and assembly of hundreds of CZT/NuASIC detectors will be labor intensive and every improvement to the detector integration and testing process will result in large reductions to schedule time and cost. Optimal operating parameters can only be finalized for each NuASIC after bonding with CZT, and must be performed in an environment that represents the detector’s in-flight conditions. To that end, NuASIC optimization and subsequent radiation source characterization will be performed in our TVAC system at reduced temperatures to limit leakage current. This will result in characterized CZT/NuASIC detectors that are each individually optimized prior to full detector plane integration for HREXI and HSEE.

6 Acknowledgements

We would like to thank Fiona A. Harrison, Jill A. Burnham, and W. Rick Cook of the California Institute of Technology along with the rest of the NuSTAR Team for developing the NuASIC and providing valuable information to facilitate its operation and testing. DPV is grateful to MA and KV for useful advice. This work was supported by NASA APRA grant NNX17AE62G. DPV is supported by the NASA FINESST Fellowship 80NSSC20K1537.

References

- [1] NAS, “Pathways to discovery in astronomy and astrophysics for the 2020s,” (2021).

- [2] J. Grindlay and et al., “The high resolution energetic x-ray imager smallsat extremes explorer,” in prep. (2023).

- [3] V. Bromm and A. Loeb, “The Expected Redshift Distribution of Gamma-Ray Bursts,” ApJ 575, 111–116 (2002).

- [4] J. Grindlay, J. Hong, B. Allen, et al., “Development of tiled imaging czt detectors for sensitive wide-field hard x-ray surveys to EXIST,” Nuclear Instruments and Methods in Physics Research A 652, 671–673 (2011).

- [5] J. Hong, B. Allen, J. Grindlay, et al., “Building large area CZT imaging detectors for a wide-field hard X-ray telescope—ProtoEXIST1,” Nuclear Instruments and Methods in Physics Research A 605, 364–373 (2009).

- [6] B. Allen, J. Hong, J. Grindlay, et al., “ProtoEXIST: advanced prototype CZT coded aperture telescopes for EXIST,” in Space Telescopes and Instrumentation 2010: Ultraviolet to Gamma Ray, M. Arnaud, S. S. Murray, and T. Takahashi, Eds., Society of Photo-Optical Instrumentation Engineers (SPIE) Conference Series 7732, 77324D (2010).

- [7] B. Allen, J. Hong, J. Grindlay, et al., “Development of the ProtoEXIST2 advanced CZT detector plane,” Proc. IEEE Nuclear Science Symp. and Medical Imaging Conf. , 4470–4480 (2011).

- [8] J. Hong, B. Allen, J. Grindlay, et al., “Tiled Array of Pixelated CZT Imaging Detectors for ProtoEXIST2 and MIRAX-HXI,” IEEE Transactions on Nuclear Science 60, 4610–4617 (2013).

- [9] J. Hong, B. Allen, J. Grindlay, et al., “Imaging Analysis of the Hard X-Ray Telescope ProtoEXIST2 and New Techniques for High-resolution Coded-aperture Telescopes,” AJ 153, 11 (2017).

- [10] W. R. Cook, J. A. Burnham, and F. A. Harrison, “Low-noise custom VLSI for CdZnTe pixel detectors,” in EUV, X-Ray, and Gamma-Ray Instrumentation for Astronomy IX, O. H. Siegmund and M. A. Gummin, Eds., Society of Photo-Optical Instrumentation Engineers (SPIE) Conference Series 3445, 347–354 (1998).

- [11] W. R. Cook, S. E. Boggs, A. E. Bolotnikov, et al., “First test results from a high-resolution CdZnTe pixel detector with VLSI readout,” in Penetrating Radiation Systems and Applications, F. P. Doty, Ed., Society of Photo-Optical Instrumentation Engineers (SPIE) Conference Series 3769, 92–96 (1999).

- [12] F. A. Harrison, W. R. Cook, H. Miyasaka, et al., “Cadmium zinc telluride pixel detectors for hard x-ray astrophysics,” in Semiconductor Radiation Detection Systems, K. Iniewski, Ed., CRC Press, Boca Raton, FL (2010). Chapter 3 Section 4.

- [13] F. A. Harrison, W. W. Craig, F. E. Christensen, et al., “The Nuclear Spectroscopic Telescope Array (NuSTAR) High-energy X-Ray Mission,” ApJ 770, 103 (2013).

- [14] J. Hong, J. Grindlay, B. Allen, et al., “Proof of concept for through silicon vias in application-specific integrated circuits for hard x-ray imaging detectors,” Journal of Astronomical Telescopes, Instruments, and Systems 7, 026001 (2021).

- [15] J. Ovental, D. Malta, D. Bordelon, et al., “TSV-Last Integration to Replace ASIC Wire Bonds in the Assembly of X-Ray Detector Arrays,” Proceedings of IEEE 71st Electronic Components and Technology Conference , 170–177 (2021).

- [16] D. P. Violette, B. Allen, J. S. Hong, et al., “Efficient validation testing of Through-Silicon-Via (TSV) ASICs for CZT x-ray detectors,” in Hard X-Ray, Gamma-Ray, and Neutron Detector Physics XX, Society of Photo-Optical Instrumentation Engineers (SPIE) Conference Series 10762, 107620S (2018).

- [17] D. P. Violette, B. Allen, J. Hong, et al., “Testing station for fast screening of through silicon via-enabled application-specific integrated circuits for hard x-ray imaging detectors,” Journal of Astronomical Telescopes, Instruments, and Systems 8, 036001 (2022).

Biographies

Daniel Violette received his PhD in astronomy and astrophysics from Harvard University in 2022, where he was supported by the Future Investigators in NASA Earth and Space Science and Technology Fellowship to further develop HREXI detector sensitivity at low energies. Currently, he is a NASA postdoctoral fellow at Goddard Space Flight Center pursuing interests in high-energy time domain astrophysics and instrumentation development.

Branden Allen received his Ph.D. degree in physics from U.C. Irvine in 2007 and is currently a Senior Research Scientist at Harvard University with over 20 years of experience in the development, deployment and operation of ground- and space-based telescopes for high-energy X/-ray astronomy and planetary science. His current research is focused on the development and deployment of next generation detector systems and telescopes to probe high energy astrophysical phenomena and for future planetary exploration.

Jaesub Hong is a Senior Research Scientist at Harvard University. He has nearly 20 years of experience in development of X-ray telescopes for high energy astrophysics and planetary science. His current focus is the development of advanced hard X-ray detectors for next generation wide-field hard X-ray telescopes for time domain astrophysics and the miniature lightweight X-ray optics for planetary science. He received a Ph.D. degree in Physics from Columbia University. He has (co)authored over 40 publications.

Hiromasa Miyasaka is a staff scientist at California Institute of Technology. He received a Ph.D. in Physics (2000) from Saitama University in Japan. He has over 20 years of experience in development of particles and X-ray detectors for the cosmic ray and high-energy astrophysics. Since 2006, his work has focused on CdZnTe and CdTe detectors and readout ASIC development. He is one of the primary detector scientists for the NuSTAR mission.

Jonathan Grindlay is the Robert Treat Paine Professor of Astronomy at Harvard. He received his BA in Physics from Dartmouth (1966) and PhD in Astrophysics from Harvard (1971). He joined the Faculty in 1976 and Chaired the Department in 1985-91 and 2001-03. His primary interest is black hole time variability, accretion physics, accreting black hole (both stellar and supermassive) populations and formation as measured with wide-field coded aperture imaging X-ray telescopes (ultimately full-sky) and optical/IR imaging/spectroscopy. He has over 434 refereed Journal papers.

Figures

| Parameter | NuASIC Setting | Size (bits) | Adjustment Effect | Tuning Order |

|---|---|---|---|---|

| vnl1 bias | vnl1sel | 2 | Preamplifier standing current | 1 |

| vnl2 bias | vnl2sel | 2 | ||

| vpl2 bias | vpl2sel | 4 | Shaping amplifier pulse shape | 2 |

| vpl3 bias | vpl3sel | 4 | ||

| 4V reference | 4Vsel | 7 | Offset Preamp Voltage Ramping | 3 |

| vn1sel (bits) | vnl2sel (bits) | Designation | Normal Baseline (mV) | CPM Baseline (mV) |

|---|---|---|---|---|

| 11 | 01 | v3o1 | 647 ± 2 | 630 ± 2 |

| 11 | 00 | v3o0 | 731 ± 2 | 696 ± 2 |

| 10 | 10 | v2o2 | 631 ± 2 | 615 ± 2 |

| 01 | 11 | v1o3 | 634 ± 2 | 620 ± 2 |

| 01 | 01 | v1o1 | 708 ± 2 | 677 ± 2 |

| 00 | 11 | v0o3 | 669 ± 2 | 646 ± 1 |

| 00 | 10 | v0o2 | 698 ± 2 | 674 ± 2 |

| vpl2sel (bits) | vpl3sel (bits) | Designation | Reset Time (s) | Magnitude (mV) |

|---|---|---|---|---|

| 1011 | 0100 | Default | 60 | 3278 12 |

| 1010 | 0100 | vpl2sel - 1 | 30 | 3273 12 |

| 1100 | 0100 | vpl2sel + 1 | 100 | 3278 12 |

| 1011 | 0011 | vpl3sel - 1 | 30 | 3276 15 |

| 1011 | 0101 | vpl3sel + 1 | 100 | 3284 8 |