On-chip Integration of Si/SiGe-based Quantum Dots and Switched-capacitor Circuits

Abstract

Solid-state qubits integrated on semiconductor substrates currently require at least one wire from every qubit to the control electronics, leading to a so-called wiring bottleneck for scaling. Demultiplexing via on-chip circuitry offers an effective strategy to overcome this bottleneck. In the case of gate-defined quantum dot arrays, specific static voltages need to be applied to many gates simultaneously to realize electron confinement. When a charge-locking structure is placed between the quantum device and the demultiplexer, the voltage can be maintained locally. In this study, we implement a switched-capacitor circuit for charge-locking and use it to float the plunger gate of a single quantum dot. Parallel plate capacitors, transistors and quantum dot devices are monolithically fabricated on a Si/SiGe-based substrate to avoid complex off-chip routing. We experimentally study the effects of the capacitor and transistor size on the voltage accuracy of the floating node. Furthermore, we demonstrate that the electrochemical potential of the quantum dot can follow a 100 Hz pulse signal while the dot is partially floating, which is essential for applying this strategy in qubit experiments.

Silicon spin qubits based on gate-defined quantum dots have recently been realized on Si/SiGe substrates with high fidelity Maune et al. (2012); Kawakami et al. (2014); Zajac et al. (2018); Watson et al. (2018); Yoneda et al. (2018); Xue et al. (2019). Given their compatibility with current semiconductor fabrication techniques and potential for easy integration with classical electronics, these quantum dots are considered to be a promising basis for quantum computers Pillarisetty et al. (2018); Eriksson, Coppersmith, and Lagally (2013); Loss and DiVincenzo (1998). Nevertheless, a fault-tolerant quantum computer requires millions of qubits Fowler et al. (2012). Even if quantum dots are designed to be identical, the required gate bias voltage still differs among the dots due to non-uniformities in the substrate and variations during the fabrication process. In a standard operating mode, two gates are used to control each quantum dot on average and each gate is connected to a separate room temperature digital-to-analog converter (DAC) through the bond wires from the chip to the sample carrier and the dilution refrigerator wiring. However, this linear approach clearly poses a bottleneck to scaling up the number of qubits. By comparison, today’s classical processor chips have only about 2000 contact pins, while billions of transistors can be integrated and operated on a single chip. This large ratio between active components and pins is described by Rent’s rule and is made possible by implementing shared control methodsFranke et al. (2019). In order to operate the millions of qubits for practical quantum computation, similar methods will therefore have to be implemented in quantum integrated circuits.

Inspired by the classical dynamic random-access memory (DRAM) matrix that uses word lines and bit lines to address a large number of storage cells Keeth et al. (2007), proposals for controlling spin qubits using word and bit lines exist Hill et al. (2015); Vandersypen et al. (2017); Veldhorst et al. (2017); Li et al. (2018); Boter et al. (2019). Another concept that can be borrowed from DRAM is charge-locking, which, when combined with demultiplexers, allows to significantly reduce the number lines going off-chip Puddy et al. (2015); Vandersypen et al. (2017); Veldhorst et al. (2017); Pauka et al. (2019). In DRAM, the stored voltage encodes a “0” or “1”, according to a threshold. In contrast, the voltage maintained on a quantum dot gate needs to be a precise analog value. The required precision of such a stored voltage ranges from 1 V to 1 mV, depending on the gate function and coupling of the gate to the dot potential Vandersypen et al. (2017); Boter et al. (2019). Charge-locking is thus used in the form of a sample-and-hold circuit, when the input line is electrically detached, the gate of the quantum dot is floating and the voltage maintains there for a certain period. Although the primary role for DC gates of quantum dots is to achieve electron confinement, additional voltage pulses must be applied to these gates for qubit experiments. For example, in a commonly used single-shot readout method to determine the state of an electron spin, a few kHz signal is applied to the gate to load, read and empty a quantum dot Elzerman et al. (2004); Morello et al. (2010). When a switched-capacitor (SC) circuit is integrated with these gates as an interface, the extra transistor or capacitor should not affect the voltage pulses arriving at the quantum dot gates. Prototypes have been made with on-chip or off-chip integrated floating gate circuits and GaAs quantum dots Puddy et al. (2015); Pauka et al. (2019). For silicon-based quantum dots, switching circuits have been integrated with quantum devices on-chip Al-Taie et al. (2013); Ward et al. (2013). In addition, charge-storage devices and quantum devices have been fabricated using the same CMOS process and connected through wire bonds Schaal et al. (2018, 2019). However, in silicon a fully on-chip integrated solution, without the need for wire bonds, is still waiting to be achieved.

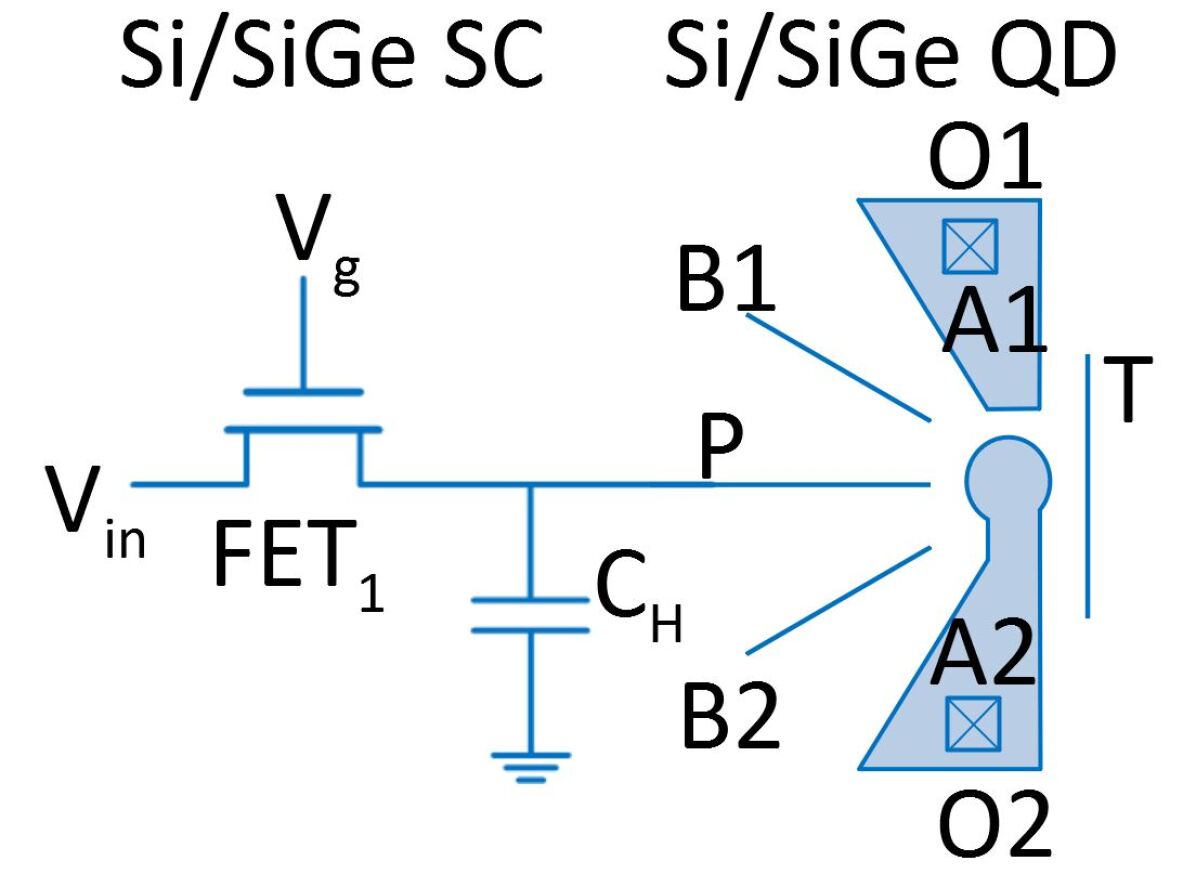

In this study, we integrate a switched-capacitor circuit containing an n-type transistor and a holding capacitor with a single quantum dot on a Si/SiGe-based substrate. We analyze the parameters that affect the variability of the floating gate voltage and experimentally study the impact of the size of the capacitor and the transistor. In addition, we apply a pulsed voltage to one of the quantum dot gates while floating another gate, as a relevant test for qubit measurements.

The impact of the design parameters on the floating node voltage accuracy as described in the literature provides guidance for our choices of device dimensions (see Fig.1(a)). We first review two mechanisms that lead to a random error in the floating node voltage, and next describe two mechanisms that produce a systematic error. As we shall see, in general a larger holding capacitance reduces these errors, but it also increases the footprint and power dissipation, both of which can limit scalability as well Franke et al. (2019).

Fundamentally, the voltage resolution of a floating node is limited by the electron charge, , as

| (1) |

where is the total capacitance of the floating node to ground. It is dominated by the holding capacitor in our case. In order to keep below 1 V, should be larger than 160 fF.

Next, thermal noise is present due the transistor channel resistance when the transistor (FET1) in a switched-capacitor circuit is switched on. The random thermal noise voltage is maintained on the holding capacitor after switching off the transistor. The root-mean-square (RMS) noise voltage on the capacitor is calculated as Brodersen, Gray, and Hodges (1979)

| (2) |

For instance, to obtain a noise level below 1 V at a temperature of 10 mK, the holding capacitance must exceed 138 fF.

A first systematic offset in the floating node voltage is caused by channel charge injection. This effect refers to the charges that get redistributed to the drain and source upon switching a transistor offRazavi (2001); Johns and Martin (1997). Under the assumption that charges split equally to the source and drain, the error in the stored voltage on the floating node can be expressed as

| (3) |

with the capacitance between the transistor gate and channel, the “on” voltage on the gate of FET1, the input voltage indicated in Fig.1(a), and the threshold voltage is the voltage difference between gate and source/drain at which charges begin to accumulate in the channel. For instance, when is set 0.1 V higher than , the holding capacitance needs to be 50 times larger than the transistor channel capacitance to keep below 1 mV.

Another factor that introduces systematic offsets in the maintained voltage is the parasitic capacitance from the transistor gate to the floating node. In series with the holding capacitance, it shifts the voltage on the floating node by an amount that depends on the voltage on the gate of FET1, given by Razavi (2001); Johns and Martin (1997)

| (4) |

where is the switching range used to turn the transistor on and off (). Taking as 1 V, the ratio of to should exceed 1000 to keep below 1 mV.

Importantly, different from the random variations in the floating gate voltage, the systematic shifts can be accounted for in the calibration phase, hence they do not impose strict requirements on .

Turning now to power dissipation, the heat generated from the on-resistance of FET1 and the parasitic resistance on the leakage path can be expressed as

| (5) |

where and are the high and low voltages on the holding capacitor during operation, and is the switching frequency of the transistor. Note that is proportional to the holding capacitance. If we refresh the floating node to compensate a 1 mV drop with a 1 Hz frequency, the power dissipation of a single cell is W when the holding capacitor is 1 pF. This is orders of magnitude smaller than the heat dissipated upon switching in the resistance in the line between the pulse generator and the transistor gate, which is given by

| (6) |

For a transistor with 0.01 pF channel capacitance and 1 V switching range, the power dissipated on the signal line to its gate is W. Even if we assume that this power is entirely dissipated on-chip, it would still allow floating gate voltages to be maintained assuming 100 W available cooling power at the chosen operating temperature.

Making the transistors smaller reduces and , which reduces switching power dissipation as well as the systematic shifts in the floating gate voltage. However, secondary effects appear when the device is scaled down. For instance, when the channel width is below 1 m, the threshold voltage increases due to the narrow-channel effect Neamen (2012); Lu et al. (2016). Then a higher gate voltage is required to turn on the transistor which is more likely to cause hysteresis and breakdown.

| Device | Device | Device | |

|---|---|---|---|

| size (m m) | 1515 | 1515 | 100100 |

| (pF) | 0.697 | 0.697 | 30.98 |

| FET1 size (m m) | 1010 | 101 | 101 |

| (pF) | 0.171 | 0.022 | 0.022 |

| (fF) | 30 | 3.9 | 3.9 |

| Expected (mV) | 53.65 | 2.67 | 0.08 |

| Expected (mV) | 9.3-26.4 | 2.9-3.5 | 0.04-0.08 |

| (V) | 0.44 | 0.44 | 0.06 |

| (V) | 0.23 | 0.23 | 0.0052 |

| Measured shift (mV) | 44-48 | 2.8-5.4 | 0.5-1 |

Based on the above considerations, we made three devices with the same quantum dot design but different transistor and holding capacitor sizes and compared their voltage variations on the floating node both theoretically and experimentally. The device dimensions are listed in Table 1 (see also Appendix A). One practical consideration for the length of the transistor is the lateral diffusion of the implantation region, which is estimated to be 0.4 m in this process. The transistor channel length is chosen to be 10 m to reduce the effect of lateral diffusion on the actual length of the channel, though fundamentally the length could be much reduced.

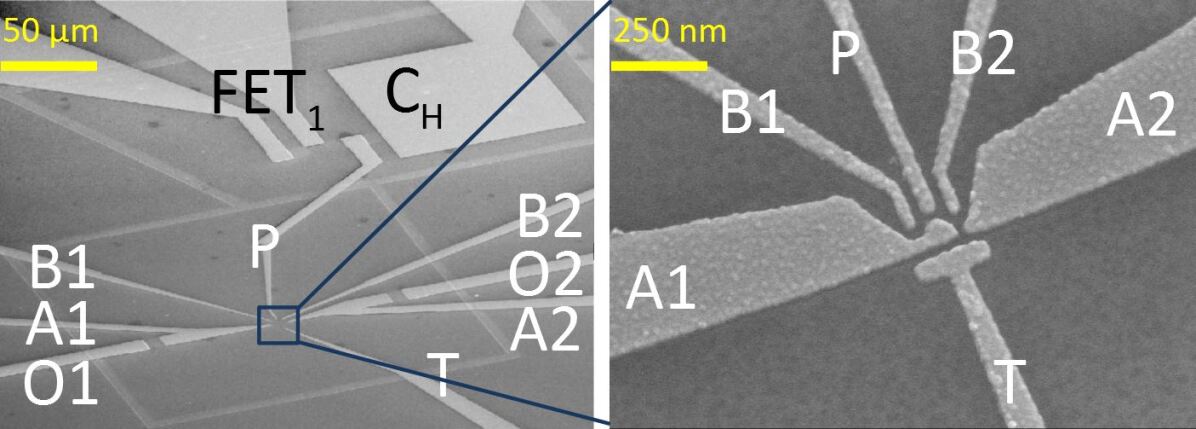

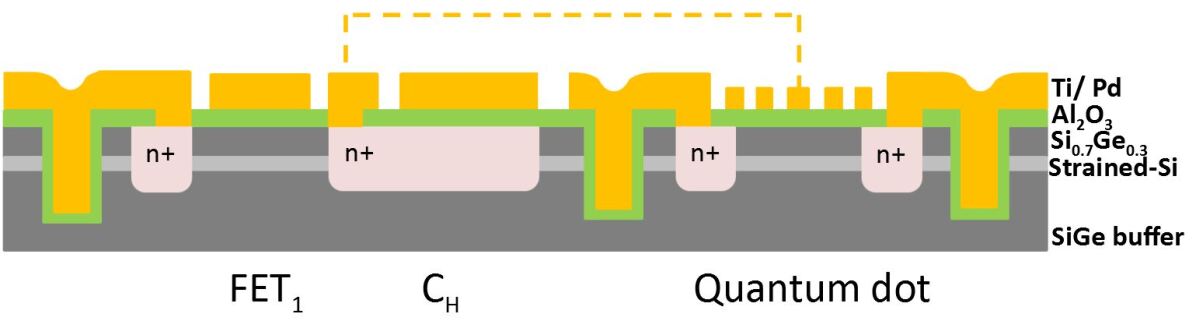

For all devices, the quantum dot, transistor, and capacitor were integrated on a Si0.7Ge0.3/strained-Si/buffered-SiGe heterostructure substrate Samkharadze et al. (2018). For the quantum dot, we used a single patterned metal layer to define the potential landscape that confines electrons. The top plate of the capacitor is formed by a metal gate and the bottom plate by a heavily implanted region in the semiconductor, with a dielectric separating the plates. The transistor is a field-effect transistor with the buried quantum well acting as the channel (see Fig.1(b)).

The fabrication process began with the definition of markers followed by phosphorus ion implantation to create reservoirs for the quantum dots, the source and drain of the transistors, and the electrodes for the capacitors. This was followed by rapid thermal annealing at 700 C to activate the dopants. Trenches of 100 nm deep and 10 m wide were subsequently etched into the Si/SiGe substrate to isolate the devices from each other. A 20 nm Al2O3 layer was then grown via atomic layer deposition to form the gate oxide for both quantum dots and transistors. Finally, we used electron beam lithography and lift-off to pattern an electron-beam evaporated 5/15 nm Ti/Pd stack to define the quantum dot gates, followed by patterning of a 5/195 nm Ti/Pd film for the transistor gate, the top electrode of the capacitor and the leads and pads of the quantum dot. Fig.1(c) shows the SEM image of one of the final devices (Device in Table 1). Details regarding the separate characterization of the single quantum dot and the transistor are described in Appendix B.

We mounted the device in a dilution refrigerator operating at a base temperature below 10 mK and at zero magnetic field. All current measurements through the quantum dot are performed with a 100 V source-drain bias applied across the quantum dot.

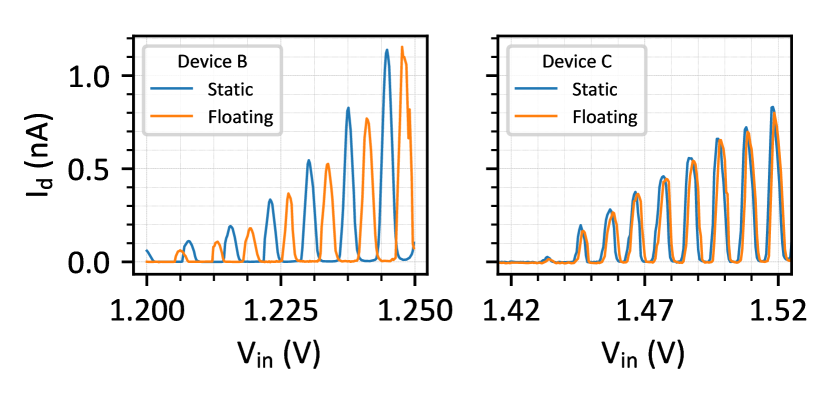

As a reference, the device was first tested in static mode with gate not floating (blue traces in Fig.2). The current through the quantum dot was experimentally measured while the transistor was conducting. In the floating mode tests, we first turned on FET1 to charge the holding capacitor and then turned it off. After 10 ms, we measured the current through the quantum dot while gate was floating. As shown in Fig.2 (and Fig. S1 for device ), the patterns of the Coulomb peaks measured in floating mode were consistent with those measured in static mode, but shifted in . Table 1 summarizes the expected and measured voltage shifts. The measured dependence of gate voltage shift versus dimensions matches the predicted trend very well, with device showing the largest shifts and device the smallest shifts.

Nevertheless, there are still variations between the measured and expected voltage shifts. We here discuss this difference for device . First we note that the average voltage decay rate for device in the first 40 seconds after opening the transistor was approximately 2.8 V/s (see Appendix C). This very low leakage rate compared to commercial DRAM is possible owing to the low operating temperature. The voltage shift on the floating gate due to leakage through the holding capacitor is thus negligible during the 10 ms interval between the moment the transistor is opened and the time of measurement. We will therefore compare the measured voltage shifts to those expected based on Eqs. 1-4. Fig. S6(b) in Appendix F shows the measured voltage shifts for the consecutive Coulomb peaks for device . The overall trend of peak shift versus matches well with Eq. 3, expressing charge injection from the channel, for the five Coulomb peaks at the highest (the leftmost peak is shifted more than expected). The additional overall systematic shift is smaller than that expected based on Eq. 4 (the transistor gate voltage coupling in through the parasitic gate-source capacitance), possibly in part due to deviations in the estimated dielectric thickness or constant. In addition, the individual shifts do fluctuate around the overall linear trend by about mV (see Appendix E). By comparison, the random shifts expected from charge quantization and thermal noise (Eqs. 1-2) are below 1 V. However, the measured voltage fluctuations match well with the measured 1/ noise caused by background charge fluctuations modulating the dot potential. The Coulomb peak measurement took a few minutes to complete and the 1/ noise amplitude at 0.01 Hz is indeed of order mV/ (see Appendix D).

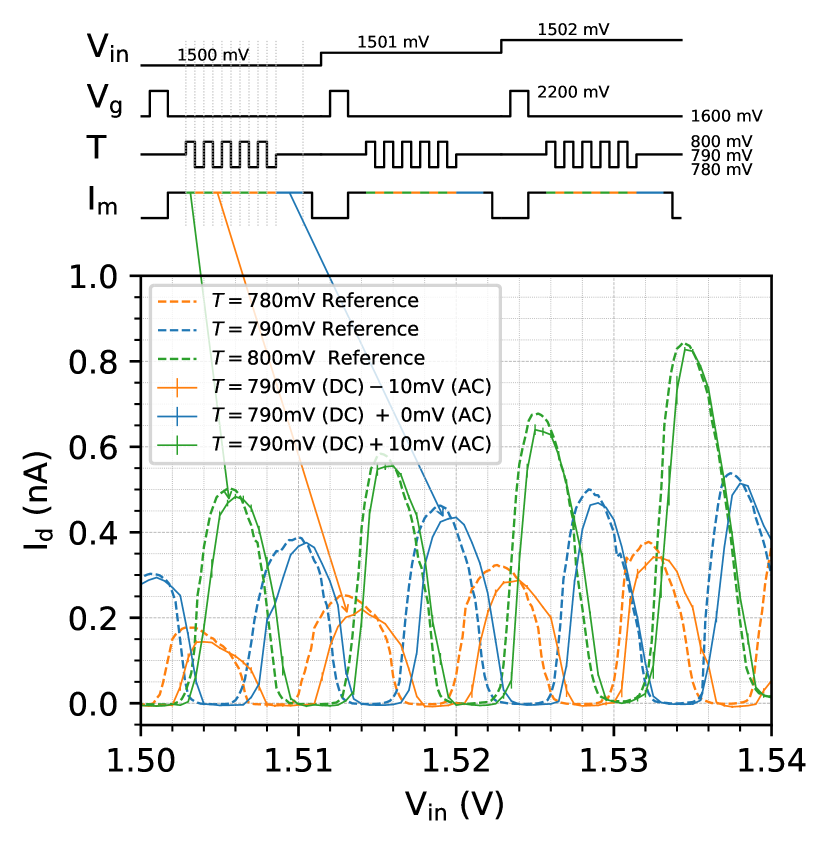

For qubit operation and readout, gate voltage pulses must be applied to one or more of the quantum dot gates. We now test the compatibility of applying such pulses with a switched-capacitor circuit present and operated in floating mode. In principle the voltage pulses can be applied either to a floating gate (e.g. via the holding capacitor) or to another gate. Either way, the question is to what extent the presence of the capacitor and transistor that form the SC circuit distorts the waveform.

Here we perform a preliminary test for voltage pulses applied to a gate that is not floating. Limited by the 1 kHz sampling rate of the current measurement, we provided a 100 Hz square wave to gate (indicated in Fig. 1(a)) of device , and check whether the electrochemical potential of the quantum dot is able to follow the signal while gate is floating. The sequence of the experiment is depicted in Fig.3. The input voltage is stepped through a range that covers several Coulomb peaks. For each , we first floated gate by setting from “high” to “low”. Then a 100 Hz, 10 mV pulse signal was applied to gate through a bias tee during 100 ms, adding to a 790 mV DC bias voltage, while we continuously measured the current flowing through the quantum dot. The current through the dot corresponding to the two stages of the voltage pulse, as well as the current during a subsequent time interval without gate voltages pulses, were extracted separately and compared to the static mode measurement results as shown in Fig.3. The Coulomb peak patterns were consistent with the respective reference measurements. The 0.6-1.0 mV voltage shift of the center peaks (blue solid versus dotted traces) is in agreement with the expected shift from channel charge injection and parasitic capacitance of the transistor upon switching off. Furthermore, the peaks obtained while applying a 100 Hz square pulse overlap closely with their expected positions, see the green and orange solid and dotted lines. The 0.6 mV larger average shift for the orange versus the green solid lines indicates that the square pulse amplitude at the gate is slightly larger than the intended mV, which is explained by a deviation (within the specified tolerance) of values of the attenuators placed in the transmission line connected to gate . These results show that the voltage pulses on gate were not affected by the switched-capacitor circuit and by floating gate . Based on electric circuit simulations (see Appendix G) that include the various capacitors discussed in the text, we expect the large capacitor that stores the floating node voltage (on gate ) not to impact the modulation of the dot potential in response to a pulse on gate until at least 20 GHz.

In summary, in this study we demonstrated that a switched-capacitor circuit placed between a quantum dot and demultiplexer can function as a local voltage source. The effect of channel charge injection and gate-source capacitive coupling introduce a systematic offset on the sampled voltage, which can be reduced if desired by using a larger holding capacitor and a smaller transistor. In the present measurements, random offsets in the stored voltage are dominated by 1/ noise in the dot potential. Finally, we show that floating a quantum dot gate does not impact the effect of (slow) voltage pulses applied to another quantum dot gate.

Acknowledgements.

We thank Mark Eriksson for useful discussions, Stephan Philips for the design of the PCB onto which the sample was mounted and Francisco Carrasco for assistance with sample fabrication. We acknowledge financial support by Intel Corporation and the QuantERA ERA-NET Cofund in Quantum Technologies implemented within the European Union’s Horizon 2020 Programme.Data Availability Statement

The data that supports the findings of this study are available within the article and its supplementary material.

References

- Maune et al. (2012) B. M. Maune, M. G. Borselli, B. Huang, T. D. Ladd, P. W. Deelman, K. S. Holabird, A. A. Kiselev, I. Alvarado-Rodriguez, R. S. Ross, A. E. Schmitz, M. Sokolich, C. A. Watson, M. F. Gyure, and A. T. Hunter, “Coherent singlet-triplet oscillations in a silicon-based double quantum dot,” Nature 481, 344–347 (2012).

- Kawakami et al. (2014) E. Kawakami, P. Scarlino, D. R. Ward, F. R. Braakman, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, “Electrical control of a long-lived spin qubit in a si/sige quantum dot,” Nature Nanotechnology 9, 666–670 (2014).

- Zajac et al. (2018) D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, “Resonantly driven cnot gate for electron spins,” Science 359, 439–442 (2018).

- Watson et al. (2018) T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, “A programmable two-qubit quantum processor in silicon,” Nature 555, 633–637 (2018).

- Yoneda et al. (2018) J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, “A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%,” Nature Nanotechnology 13, 102–106 (2018).

- Xue et al. (2019) X. Xue, T. F. Watson, J. Helsen, D. R. Ward, D. E. Savage, M. G. Lagally, S. Coppersmith, M. A. Eriksson, S. Wehner, and L. M. K. Vandersypen, “Benchmarking gate fidelities in a si / sige two-qubit device,” Physical Review X 9, 201011 (2019).

- Pillarisetty et al. (2018) R. Pillarisetty, N. Thomas, H. C. George, K. Singh, J. Roberts, L. Lampert, P. Amin, T. F. Watson, G. Zheng, J. Torres, M. Metz, R. Kotlyar, P. Keys, J. M. Boter, J. P. Dehollain, G. Droulers, G. Eenink, R. Li, L. Massa, D. Sabbagh, N. Samkharadze, C. Volk, B. P. Wuetz, A.-M. Zwerver, M. Veldhorst, G. Scappucci, L. M. K. Vandersypen, and J. S. Clarke, “Qubit device integration using advanced semiconductor manufacturing process technology,” in IEEE International Electron Devices Meeting (IEDM) (2018).

- Eriksson, Coppersmith, and Lagally (2013) M. Eriksson, S. Coppersmith, and M. Lagally, “Semiconductor quantum dot qubits,” MRS Bulletin 38, 794–801 (2013).

- Loss and DiVincenzo (1998) D. Loss and D. P. DiVincenzo, “Quantum computation with quantum dots,” Phys. Rev. A 57, 120–126 (1998).

- Fowler et al. (2012) A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, “Surface codes: Towards practical large-scale quantum computation,” Phys. Rev. A 86, 032324 (2012).

- Franke et al. (2019) D. P. Franke, J. S. Clarke, L. M. K. Vandersypen, and M. Veldhorst, “Rent’s rule and extensibility in quantum computing,” Microprocessors and Microsystems 67, 1–7 (2019).

- Keeth et al. (2007) B. Keeth, R. J. Baker, B. Johnson, and F. Lin, DRAM Circuit Design. Fundamental and High-Speed Topics (Wiley-IEEE Press, 2007).

- Hill et al. (2015) C. Hill, E. Peretz, S. Hile, M. House, M. Fuechsle, S. Rogge, M. Simmons, and L. Hollenberg, “A surface code quantum computer in silicon,” Science Advances 1, e1500707 (2015).

- Vandersypen et al. (2017) L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, “Interfacing spin qubits in quantum dots and donors - hot, dense, and coherent,” npj Quantum Information 3, 34 (2017).

- Veldhorst et al. (2017) M. Veldhorst, H. Eenink, C. Yang, and A. Dzurak, “Silicon cmos architecture for a spin-based quantum computer,” Nature Communications 8, 1766 (2017).

- Li et al. (2018) R. Li, L. Petit, D. P. Franke, J. P. Dehollain, J. Helsen, M. Steudtner, N. K. Thomas, Z. R. Yoscovits, K. J. Singh, S. Wehner, L. M. K. Vandersypen, J. S. Clarke, and M. Veldhorst, “A crossbar network for silicon quantum dot qubits,” Science Advances 4, EAAR 3960 (2018).

- Boter et al. (2019) J. M. Boter, J. P. Dehollain, G. van Dijk, T. Hensgens, R. Versluis, J. S. Clarke, M. Veldhorst, F. Sebastiano, and L. M. K. Vandersypen, “A sparse spin qubit array with integrated control electronics,” in IEEE International Electron Devices Meeting (IEDM) (IEEE, New York, 2019) pp. 31.4.1–31.4.4.

- Puddy et al. (2015) R. K. Puddy, L. W. Smith, H. Al-Taie, C. H. Chong, I. Farrer, J. P. Griffiths, D. A. Ritchie, M. J. Kelly, M. Pepper, and C. G. Smith, “Multiplexed charge-locking device for large arrays of quantum devices,” Applied Physics Letters 107, 143501 (2015).

- Pauka et al. (2019) S. J. Pauka, K. Das, R. Kalra, A. Moini, Y. Yang, M. Trainer, A. Bousquet, C. Cantaloube, N. Dick, G. C. Gardner, M. J. Manfra, and D. J. Reilly, “A cryogenic interface for controlling many qubits,” (2019), arXiv:1912.01299v1.

- Elzerman et al. (2004) J. M. Elzerman, R. Hanson, L. H. Willems van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, “Single-shot read-out of an individual electron spin in a quantum dot,” Nature 430, 431–435 (2004).

- Morello et al. (2010) A. Morello, J. J. Pla, F. A. Zwanenburg, K. W. Chan, K. Y. Tan, H. Huebl, M. Möttönen, C. D. Nugroho, C. Yang, J. A. van Donkelaar, A. D. C. Alves, D. N. Jamieson, C. C. Escott, L. C. L. Hollenberg, R. G. Clark, and A. S. Dzurak, “Single-shot readout of an electron spin in silicon,” Nature 467, 687–691 (2010).

- Al-Taie et al. (2013) H. Al-Taie, L. W. Smith, B. Xu, P. See, J. P. Griffiths, H. E. Beere, G. A. C. Jones, D. A. Ritchie, M. J. Kelly, and C. G. Smith, “Cryogenic on-chip multiplexer for the study of quantum transport in 256 split-gate devices,” Applied Physics Letters 102, 243102 (2013).

- Ward et al. (2013) D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, and M. A. Eriksson, “Integration of on-chip field-effect transistor switches with dopantless si/sige quantum dots for high-throughput testing,” Applied Physics Letters 102, 213107 (2013).

- Schaal et al. (2018) S. Schaal, S. Barraud, J. J. L. Morton, and M. F. Gonzalez-Zalba, “Conditional dispersive readout of a cmos single-electron memory cell,” Phys. Rev. Applied 9, 054016 (2018).

- Schaal et al. (2019) S. Schaal, A. Rossi, V. N. Ciriano-Tejel, T.-Y. Yang, S. Barraud, J. J. L. Morton, and M. F. Gonzalez-Zalba, “A cmos dynamic random access architecture for radio-frequency readout of quantum devices,” Nature Electronics 2, 236–242 (2019).

- Brodersen, Gray, and Hodges (1979) R. W. Brodersen, P. R. Gray, and D. A. Hodges, “Mos switched-capacitor filters,” Proceedings of the IEEE 67, 61–75 (1979).

- Razavi (2001) B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill Education, 2001).

- Johns and Martin (1997) D. A. Johns and K. Martin, Analog Integrated Circuit Design (John Wiley and Sons, 1997).

- Neamen (2012) D. A. Neamen, Semiconductor Physics and Devices: Basic Principles (McGraw-Hill, 4th edition, 2012).

- Lu et al. (2016) T. M. Lu, J. K. Gamble, R. P. Muller, E. Nielsen, D. Bethke, G. A. Ten Eyck, T. Pluym, J. R. Wendt, J. Dominguez, M. P. Lilly, M. S. Carroll, and M. C. Wanke, “Fabrication of quantum dots in undoped heterostructures using a single metal-gate layer,” Applied Physics Letters 109, 093102 (2016).

- Samkharadze et al. (2018) N. Samkharadze, G. Zheng, N. Kalhor, D. Brousse, A. Sammak, U. C. Mendes, A. Blais, G. Scappucci, and L. M. K. Vandersypen, “Strong spin-photon coupling in silicon,” Science 359, 1123–1127 (2018).

- Elzerman et al. (2006) J. M. Elzerman, R. Hanson, L. H. Willems van Beveren, L. M. K. Vandersypen, and L. P. Kouwenhoven, “Semiconductor few-electron quantum dots as spin qubits,” in Quantum Computing in Solid State Systems, edited by B. Ruggiero, P. Delsing, C. Granata, Y. Pashkin, and P. Silvestrini (Springer New York, 2006) pp. 298–305.

- Sheu and Hu (1984) B. J. Sheu and C. C. Hu, eds., IEEE J. Solid-State Circuits, sc-19 No. 4 (1984).

- Freeman, Schoenfield, and Jiang (2016) B. M. Freeman, J. S. Schoenfield, and H. Jiang, “Comparison of low frequency charge noise in identically patterned and quantum dots,” Applied Physics Letters 108, 253108 (2016).