2023

[1]Jesús D. Cifuentes [1,2]Andre Saraiva

1]\orgdivSchool of Electrical Engineering and Telecommunications, \orgnameUniversity of New South Wales, \orgaddress\postcodeNSW 2052, \citySydney, \stateNSW, \countryAustralia

2]\orgdivDiraq, \orgaddress\citySydney, \stateNSW, \countryAustralia

3]\orgdivSolid State Physics Laboratory, Department of Physics, \orgnameETH Zurich, \orgaddress\postcode8093, \countrySwitzerland

4]\orgdivSchool of Fundamental Science and Technology, \orgnameKeio University, \orgaddress \stateYokohama, \countryJapan

5]\orgdivLeibniz-Institut für Kristallzüchtung, \orgaddress\postcode12489, \stateBerlin, \countryGermany

6]\orgdivVITCON Projectconsult GmbH, \orgaddress\postcode07745, \stateJena, \countryGermany

7]\orgdivDepartment of Physics, \orgnameSimon Fraser University, \orgaddress \postcodeV5A 1S6, \stateBritish Columbia, \countryCanada

8]\orgdivSchool of Physics, \orgnameUniversity of New South Wales, \orgaddress\postcodeNSW 2052, \countryAustralia

Bounds to electron spin qubit variability for scalable CMOS architectures

Abstract

Spins of electrons in silicon MOS quantum dots combine exquisite quantum properties and scalable fabrication. In the age of quantum technology, however, the metrics that crowned Si/SiO2 as the microelectronics standard need to be reassessed with respect to their impact upon qubit performance. We chart spin qubit variability due to the unavoidable atomic-scale roughness of the Si/SiO2 interface, compiling experiments across 12 devices, and develop theoretical tools to analyse these results. Atomistic tight binding and path integral Monte Carlo methods are adapted to describe fluctuations in devices with millions of atoms by directly analysing their wavefunctions and electron paths instead of their energy spectra. We correlate the effect of roughness with the variability in qubit position, deformation, valley splitting, valley phase, spin-orbit coupling and exchange coupling. These variabilities are found to be bounded, and they lie within the tolerances for scalable architectures for quantum computing as long as robust control methods are incorporated.

keywords:

Variability, spin qubits, oxide roughness, scalabilityIntroduction

The interface between silicon and its oxide permeates most of the technology that enabled the digital era, and as such it is one of the most studied materials in human history. The practical process engineering advantages of silicon dioxide contrast with the complex chemistry of this material, and the decades of research that has underpinned the development of the CMOS industry. As we approach a new era of quantum technology, this know-how is largely considered a major advantage for technologies such as silicon-based spin qubits Maurand2016 . In particular, the similarity between quantum dots defined by gate electrodes on top of a silicon/silicon dioxide interface and the MOSFET transistors in materials, design, and fabrication enables the integration of manufacturing techniques exclusive to semiconductor foundries onto the scaling of quantum processors Veldhorst2017 .

| Device | Dots | Configuration | Driving |

|

Gate Material | Publications | ||

|---|---|---|---|---|---|---|---|---|

| A | P1, P2 | (1,1),(3,1),(1,3) | Antenna | Yes | Pd/Ti + ALD | gilbert_-demand_2023 | ||

| B | P2, P3 | (3,1) | Antenna | No | Pd/Ti + ALD | - | ||

| C | P2, P3 | (3,1) | Antenna | No | Pd/Ti + ALD | gilbert_-demand_2023 | ||

| D | P1, P2 | (1,3) |

|

No | Pd/Ti + ALD | vahapoglu_coherent_2022 | ||

| E | P1, P2 | (3,1) | Antenna | Yes | Al | tanttu2023 ; hansen_implementation_2022 ; stuyck_real-time_2023 | ||

| F | P2 | 1 electron | Antenna | No | Al | tanttu2023 ; gilbert_-demand_2023 |

Here, we specifically treat the case of such qubits formed in quantum dots at the Si/SiO2 interface, which are compatible with the high-yield integration of on-chip electronic components, and refer to these as CMOS qubits. We note, however, that other forms of silicon-based quantum dots can be manufactured, for instance by leveraging a Si/SiGe quantum well philips_universal_2022 . These materials present their own complex challenges and advantages and impose significantly different architectural choices compared to the Si/SiO2 interface, and hence are left out of this investigation.

Despite a relatively late start Veldhorst2014 , the performance of silicon qubits has led to fidelity levels comparable with more well-established quantum technologies like superconducting or ion-trap qubits noiri_fast_2022 ; mills_two-qubit_2022 ; Yang2019 . The recent demonstration of repeatable high fidelity two-qubit operations across three nominally identical CMOS devices tanttu2023 signals the beginning of an age focused on extensive repeatability of the high performance to achieve scaled architectures. However, despite the improvements in gate uniformity demonstrated by the integration of foundry-level manufacturing techniques zwerver_qubits_2022 , new concerns are stirred by the fragility of spins to effects that are ignored in classical transistor technology, such as variations in spin-orbit coupling (impacting one-qubit frequencies), exchange interaction (two-qubit couplings) and valley splitting (nearest excitation energy).

It is only by understanding this variability quantitatively that it is possible to develop a sensible scalable quantum processor architecture. Enabling the breakthrough applications of quantum computation requires millions of qubits to perform error correction gidney_how_2021 ; beverland_assessing_2022 , and it is infeasible to address all of these qubits with pulses catering to their particular parameters with wires individually running from the room temperature controllers. Instead, this variability must be embraced and corrected through the combination of on-chip electronics operating at cryogenic temperatures Veldhorst2017 ; vandersypen_interfacing_2017 , and robust quantum control pulses that will be shared among several qubits hansen_pulse_2021 ; hansen2023entangling . Designing control cells that can offset qubit properties across a large range and with sufficient accuracy is only possible if the electric tunability compensates for the range of variations. As we will discuss in this paper, this interplay between variability and tunability differs between qubit parameters (one-qubit frequencies and two-qubit couplings, etc), so a different control strategy must be adopted in each scenario.

Qubit variability is caused by the same factors that affect conventional CMOS technology, such as strain, fabrication defects, accidental introduction of charged impurities in the oxide, interface roughness, and so on asenov_simulation_2009 . Industrial foundries focus most of their efforts in addressing these issues zwerver_qubits_2022 ; elsayed_low_2022 ; Intel2019 , with a central role played by the choice of materials for substrate, dielectrics, gate metals, etc Saraiva2022 .

In the centre of the discussion is the dielectric interface where the electrons are confinedLawrie2020 ; Burkard2023_semiconductor_qubits . High fidelity silicon qubits have been measured in Si/SiGe and Si/SiO2 heterostructures philips_universal_2022 ; mills_two-qubit_2022 ; noiri_fast_2022 ; Yang2019 ; tanttu2023 . In the case of Si/SiGe heterostructures, a thin layer of uniaxially strained silicon binds the electron due to the conduction band shift caused by the strain when compared to the relaxed SixGe1-x alloy. The Si/SiGe interface provides, in general, reduced levels of interfacial disorder compared to that of Si/SiO2 Lawrie2020 . Potential shortcomings of Si/SiGe technology are the reduced gate control when compared to MOS devices and the limited tolerance of the material stack to high temperature annealing processes, commonly adopted in the CMOS industry. More information on this material and its comparison to oxides can be found in Ref. Saraiva2022 . In the context of spin qubit variability, comparing an oxide interface to Si/SiGe is hard because the nature of disorder in the two materials is different - alloy disorder and miscut angles in SiGe, compared to amorphous oxidation in SiMOS. Moreover, the dominant effect of spin-orbit coupling being studied here is masked by the presence of micromagnets which are commonly adopted in SiGe qubit architectures philips_universal_2022 .

In this paper, we focus on qubits at the Si/SiO2 interface. SiO2 does not have a regular lattice structure when thermally grown on the silicon surface, so the interface is atomically rough. The higher levels of interfacial disorder when compared to Si/SiGe are attributed to this roughness and to the presence of fixed charge defects that can be either at the Si/SiO2 interface, in the bulk of SiO2 or at the metal-oxide interface Lawrie2020 ; elsayed_low_2022 ; Intel2019 ; Müller_2019_traps_solids . Potential advantages are in the higher electrical tunability and compatibility with conventional CMOS technology, which benefits the integration with on-chip electronics Veldhorst2017 .

The roughness of the Si/SiO2 interface is one of the most critical sources of disorder for CMOS spin qubits jock_siliconMOS_sandia_2018 ; Veldhorst2015_spin_orbit ; Tanttu2019 ; Ruskov2018 ; Ferdous2018 ; Gamble2016 . A more recent paper indicated that a second source - charged impurities in the oxide - could dominate over interface roughness martinez_variability_2022 , at least in the case where a micromagnet is integrated to allow electron spin qubits to be driven electrically. Electric driving requires a large spin-orbit coupling, which exposes the spins to the impact of charge impurities. In this paper we focus on spin qubits driven magnetically Veldhorst2014 ; vahapoglu_coherent_2022 , which do not have this requirement. These qubits can be controlled coherently without the inclusion of micro-magnets, thus preserving the low spin-orbit coupling of electrons in silicon and protecting the spin from electric fluctuations. We will show in this paper, that under these conditions the remaining spin-orbit variability is interface-induced with charge impurities only affecting the qubit by shifting the quantum dot formation against the roughness profile of the interface.

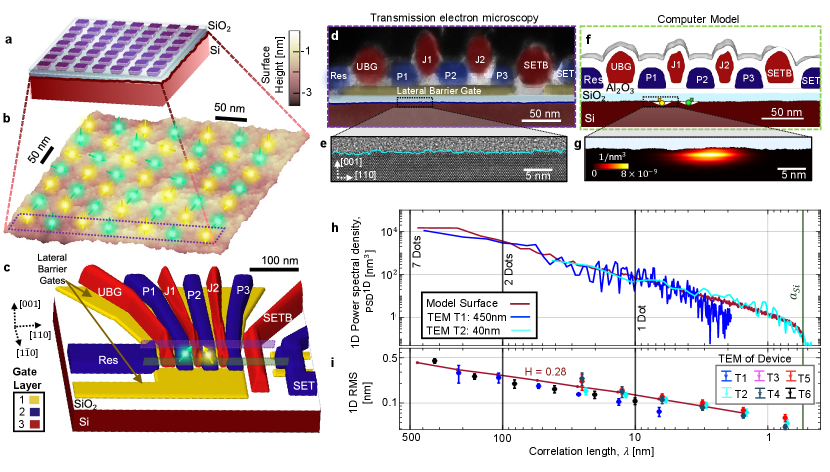

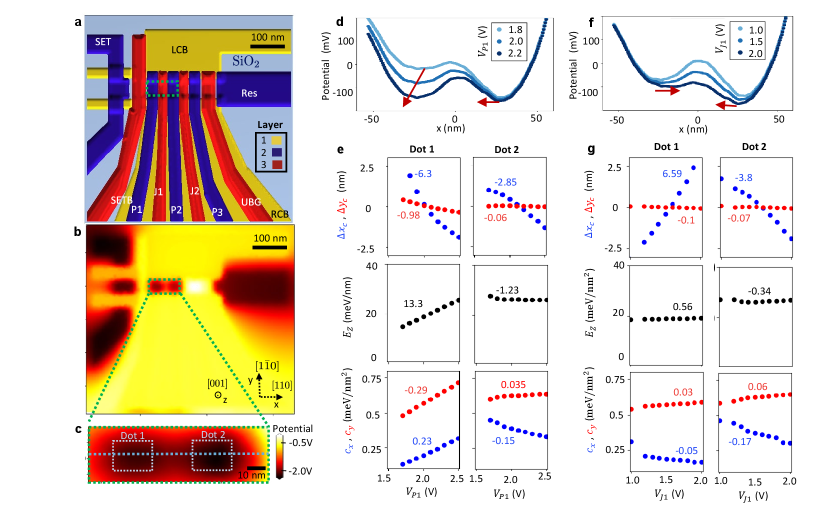

Recent advances in CMOS quantum dot fabrication allowed for sufficient yield to create a number of small-scale quantum processing units and measure their variability. This work combines measurements of 12 qubits across 6 different CMOS quantum dot devices, transmission electron microscopy (TEM) images of cross-sectional cuts of 6 other quantum dot devices and theoretical analysis of quantum properties of electrons in simulated quantum arrays of 49 quantum dots (Fig. 1a). Such a geometry allows us to study the impact of the self-affine scaling of the Si/SiO2 roughness on qubit properties at different length-scales Yoshinobu1995 (Fig. 1b). Starting from a detailed view to the device architecture, quantum dot formation, and materials interface down to the atomic scale, we predict the bounds to spin qubit variations. This prediction is compared with data from qubit devices , some of which have led to manuscripts and publications (see Table 1). All devices were fabricated with geometrically identical designs (see structure depicted in Fig. 1c) and differ only in material stack compositions and spin control methods (Table 1).

Results

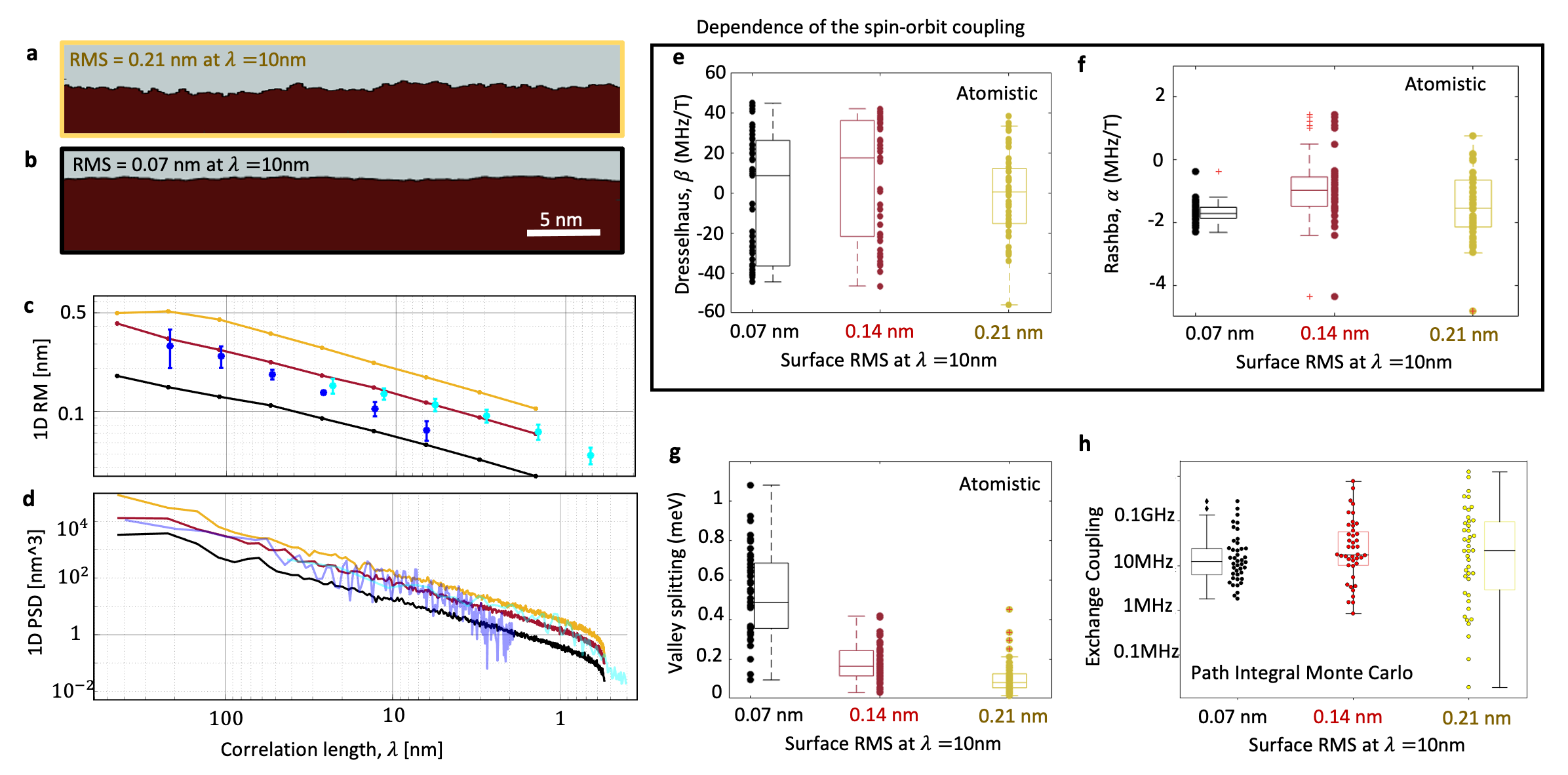

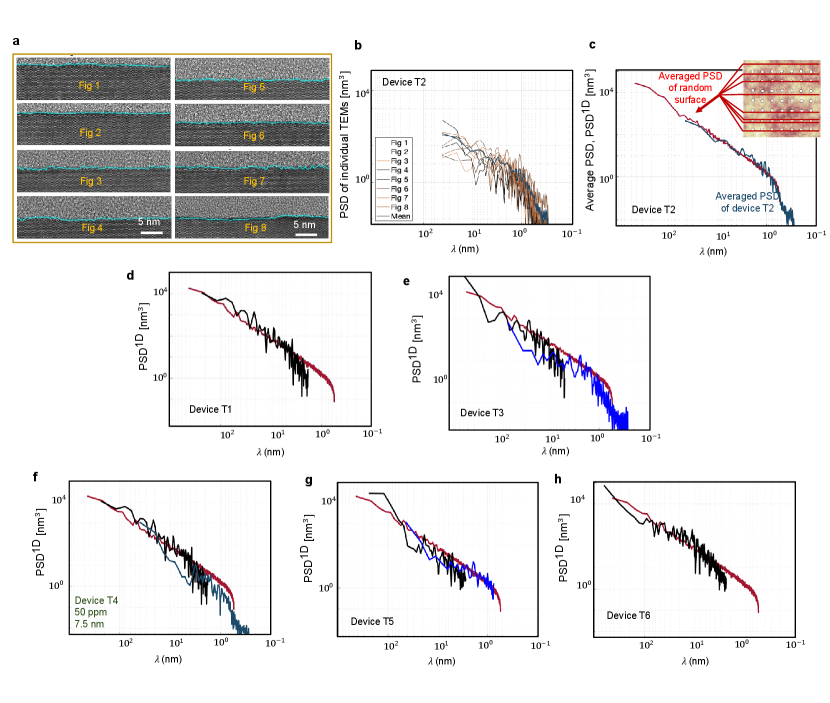

Si/SiO2 roughness The Si/SiO2 interface has an intrinsic fractal structure Yoshinobu1995 , that has not been considered in previous variability studies (Ferdous2018 ; Gamble2016 ; martinez_variability_2022 ) . Our decision to simulate a 77 dot array is motivated by understanding how this fractal scaling of the interface roughness impacts qubit properties at different length scales (see Fig. 1b). One-qubit properties, for instance, depend on the roughness obtained within the quantum dot diameter ( 15 nm), while two-qubit properties are related to the interdot distance (30-60 nm). The roughness amplitude can differ significantly between these two scales due to this fractal structure, so a quantitative characterization of the interface is necessary.

Our model of the Si/SiO2 (Fig. 1.b) is based on the roughness observed in TEM images (Fig. 1d-e) Goodnick1985 ; Yoshinobu1995 , allowing us to include more realistic features. By convolving these images with the expected face-centred cubic lattice of monocrystalline silicon we can mathematically discern the interface and analyse the roughness at different scales Goodnick1985 , quantified through its power spectral density (PSD) as a function of the in-plane correlation length scale Yoshinobu1995 . Our work incorporates a theoretical study of the realistic scale-dependent fractal structure of the roughness Yoshinobu1995 and the development of theoretical tools capable of capturing this multiscale physics in a realistic device model (Fig. 1f-g).

Combining multiple TEM images, we obtained in Fig. 1h a consistent roughness pattern characteristic of a fractal scaling down to the silicon lattice parameter of the form . We estimate a Hurst exponent of =0.28 Jacobs2017a (details in Supplementary Fig. 6 and methods section). The root-mean-square roughness also scales up with the lateral region as . As shown in Fig. 1i this roughness pattern is consistent across all devices measured, and extends up to half a micrometre . We note that these levels of roughness are typical for industry-standard interfaces Intel2019 . Our computer-generated interface in Figs. 1b,f and g was also designed to mimic these features.

A direct conclusion from Fig. 1h-i is that the size of the dots (approximately 15 nm for all devices studied) and the separation between dots (approximately 50 nm) will have a large impact on the qubit exposure to surface roughness, and that the interface distortions within a quantum dot are smaller than those between neighbouring dots. The root-mean-square (RMS) is approximately 0.15 nm within a dot (approximately 1 monolayer of the Si lattice), and almost twice for the double dot (RMS is 0.3nm, approximately 2 monolayers of the Si lattice).

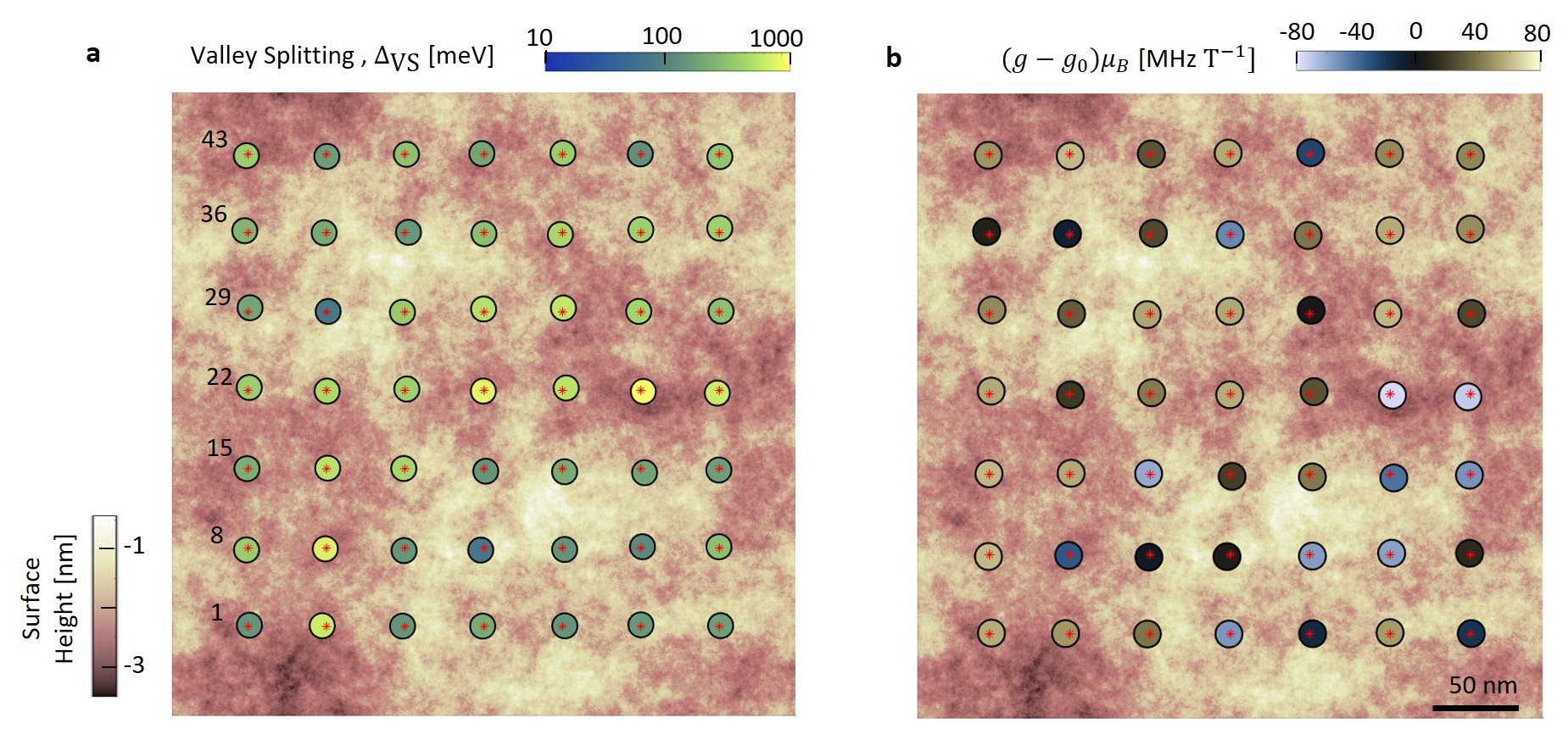

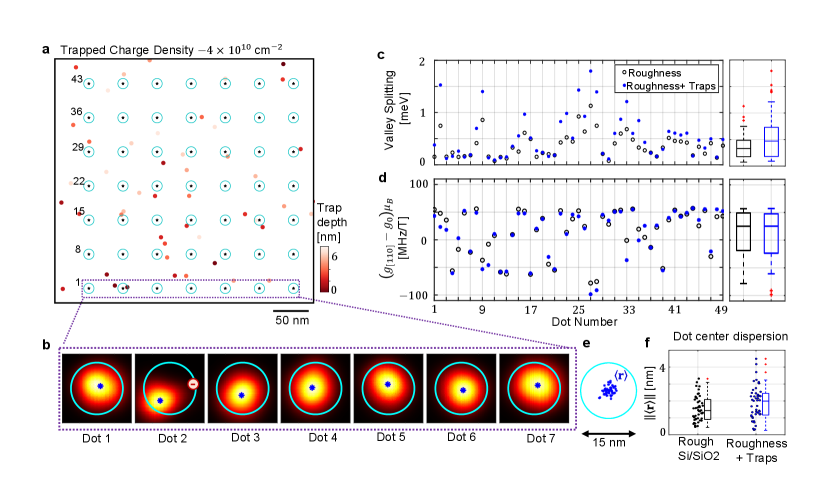

Variability of quantum dot structure and excitation energy

The consistency of this roughness pattern across devices allows to theoretically forecast its impact on qubit performance at scale. We simulate the spin qubit variability of quantum dots formed in different subsections of the computer-generated interface in Fig. 2a-b. Unless indicated differently, all quantum dots are simulated using the same electrostatic potential, which is based on COMSOL simulations of realistic digital models of our devices (see Fig. 1c-g and methods section). The only difference between simulations is the location of the quantum dots in the surface profile. Such a model allows us to incorporate the self-affine characteristic of the Si/SiO2 interface in our simulations.

In this paper, the quantum dots are simulated in a 77 grid array. Other architectures are also being explored SpiderWeb2022 , in part, because the practical design of such a dense array requires a sophisticated fabrication process with multiple metal layers to route the signals to the gates Veldhorst2017 . While dense wiring in multiple metal layers is routinely integrated in front-end-of-line industrial processes, qubit demonstrations using this integration have only recently been explored HRL_Sledge_2022 . Moreover, this dense array leaves no space for interspersed readout devices such as single-electron transistors, and would be dependent on a gate-based readout approach Gonzales_Readout_2021 or would require quantum information to be shuffled to the edges of the array for readout Peta_swap_sigillito_coherent_2019 . Our results for qubit variability are not drastically affected by the choice of a grid array, except for a small degree of nearest neighbor correlations (see Supplementary Fig. 11), which once simulated across the full 450 450 nm Si/SiO2 computer-generated interface, provides us with sufficient sampling to obtain statistical analyses accurately.

To understand how this roughness affects the quantum behaviour of electrons, it is necessary to focus on their wavefunction at the atomic scale (Fig. 2b). We use an atomistic tight binding model of Si and SiO2 which incorporates relativistic effects and the impact of a magnetic field, yielding eigenstates with realistic spin and valley structure. It can be used to calculate the ground state wavefunction and a few excited states.

Despite SiO2 not having a regular lattice structure, we simulate it by assuming an atomistically ordered virtual crystal approximation (see Methods). The material is endowed with the same lattice structure as Si and the tight-binding parameters are set to emulate the electronic structure of the interface kim_full_2011 ; Bersch2008 . This approximation allows us to simulate interface disorder atomistically as seen in Fig. 2a. In addition, we developed techniques to extract this structure and calculate properties of the disordered quantum dot that would not be obtained with a purely spectral analysis, such as the valley phase and the spin g-tensor (see Methods).

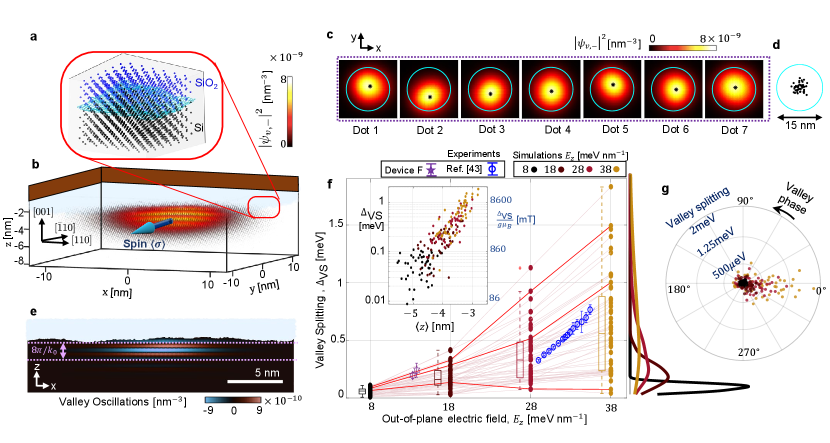

We find that the geometry explored here always leads to the successful formation of quantum dots, regardless of the local roughness profile. This is consistent with the yield of measurable quantum dots – all devices with functional gate electrodes (as determined by their influence on the charge sensing single electron transistor) could form controllable pairs of dots. Roughness mostly alters the quantum dot effective shape and centre position (Fig. 2c), with location of the electron departing from the potential minimum by less than 5 nm, with a standard deviation of 1.4 nm (Fig. 2d). The dot position in the geometry studied here is highly tunable by biasing lateral gates (approximately 5 nm/V, see Supplementary Fig. 7 and Supplementary Table 3), so that this disturbance can be corrected.

The excited orbital states are more impacted by the interface roughness. We are particularly interested in the first excited state, which corresponds to a valley excitation for a [001] Si/SiO2 interface. The conduction band valleys along crystal directions are energetically favourable due to the effective mass anisotropy, and the degeneracy between these two valleys is lifted by the sharp interface. The performance of spin qubits is strongly impacted by the interface-induced valley coupling, which creates a superposition between the two valley quantum states. This superposition creates an oscillatory behaviour at the atomic scale, which can be seen in simulations in Fig. 2e. These oscillations are known to cause variability in valley structure even for interfaces with low levels of disorder. We refer to the relative phase between valleys in this superposition as valley phase and the energy separation between the two states as valley splitting.

To have pure spin systems, valley splittings exceeding the Zeeman energy are desirable. In Fig. 2f, we show how the valley splitting can be controlled tuning the vertical electric field , comparing measurements in two devices and the results of the simulations. The surface roughness causes variability in valley splitting of over one order of magnitude for a fixed electric field. The full range of valley splittings spreads from tens of eV to a few meV, compatible with observed experimental values in CMOS devices Yang2013 ; Gamble2016 .

When comparing these valley splittings to the spin splitting, we may ignore the variability in Zeeman energy (which is only of a few parts per thousand). Therefore, if we set a relatively high electric confinement (28 meV is sufficient in our simulation) and we tune the magnetic field low enough (¡700 mT in our study), all the 49 qubits in the simulation will obey the condition of valley splitting larger than the Zeeman splitting (See inset Fig. 2f). However, the fitted distributions in Fig. 2f show that the valley splitting can sometimes be very small, even at high electric confinements. This is an exceptional event, and for low magnetic fields none of the 49 dots simulated here had valley splittings too small. However, it could potentially affect the development of large-scale quantum processors with millions of qubits as it is expected that a number of quantum dots will have the valley splitting clashing with the spin splitting. A possible solution would involve changing the number of electrons in the dot Leon2020 . In worst case scenarios, the dot must be discarded from the processor at the firmware level. A thorough discussion of the impact of this decision on error correction is presented in Ref. Nagayama_2017 .

Even with a consistently high valley splitting, qubit performance can still be impacted by variations in valley phases between neighbouring dots. The electron density will present Bloch oscillations in the direction, which are barely visible in Fig. 1f and were enhanced in Fig. 2e by taking the difference between the electron densities of both valley states (Methods). Notice that the oscillations have the same phase across the whole dot instead of conforming to the roughness of the oxide. This implies that the valley phase is well defined even in the presence of surface disorder. This phase has an impact on operations that involve two dots, such as electron tunnelling and exchange coupling, because it determines whether these valley oscillations interfere constructively or destructively tariq_impact_2022 ; Tagliaferri2018 . Fig. 2g shows the valley phases across the 49 simulated dots, revealing that dots with larger valley splittings (typically above 300 eV) tend to have similar valley phases, near zero in our definition. We speculate that this behaviour is a consequence of most dots with high valley splittings being formed in a preferred atomic layer, with similar z (see inset Fig. 2f), such that they have aligned valley phases.

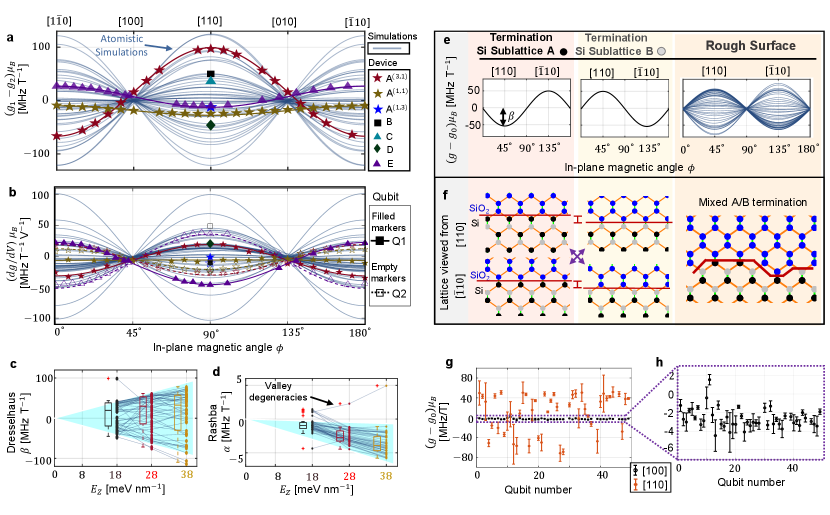

Qubit frequency variations Spin-orbit effects lead to variability in qubit frequencies of the order of 100 peV, which appears in the form of a variable factor for the spin subject to an external magnetic field. This variation represents less than 1% of the qubit frequency. The mean value of the ratio of Zeeman frequency and external magnetic field is 27.9 GHz T-1, with the differences occurring only at the order of tens of MHz T-1. This is a particularity of silicon electrons, whose spin-orbit coupling is among the smallest in all quantum dot technologies. This provides CMOS spin qubits with special protection against disorder and electric fluctuations. However, these very small g-factor variations are still important for qubit operations aimed at higher than 99.9% fidelity, and they are directly linked to the roughness of the interface at the atomic scale.

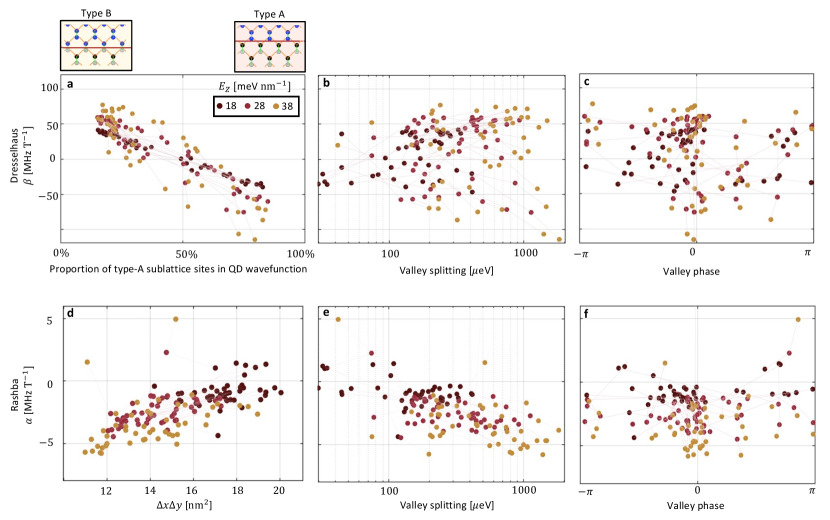

Interface-induced spin-orbit coupling has two flavours in Si/SiO2 interfaces – Rashba () and Dresselhaus () Ruskov2018 . These two can be experimentally differentiated by measuring the g-factor dependence on the in-plane magnetic field orientation Tanttu2019 . The dependence is sinusoidal with the form , where we take to be the theoretical bulk g-factor calculated from atomistic simulations including relativistic spin-orbit effects. The difference between the frequencies of any two qubits (Fig 3.a), as well as the electric field dependence (Fig 3.b have the same behaviour. All 12 qubits measured in devices A to E show behaviours consistent with this description. Qubits in the same quantum dot but with different electron numbers are considered as different in the total count, as they have substantially different g-factors (see data from device A in Fig 3.a-b). This is most likely due to different exposition to the atomic profile of the interface for electrons in different valley states. In most cases, Dresselhaus dominates both the total spin-orbit effect and its variability – with the exception of the configuration (1,1) in device A (Fig. 3.a). The Rashba coefficient is typically one order of magnitude smaller than (Fig. 3.c-d).

We explore theoretically this variability by extracting the g-tensor of electrons in disordered quantum dots from the eigenfunctions calculated by tight binding. The results of simulations, shown as solid lines in Figs. 3a and b, are then used to extract the dependence of and on the vertical electric field (Figs. 3c and d). The Dresselhaus effect emerges from breaking the lattice inversion symmetry near an interface, which explains why it is strongly dependent on the electric field that confines the electron against the oxide (Fig. 3c). The interface-induced Rashba effect is also dependent on the electric field, but at a smaller scale (Fig. 3d ). Notice that a couple of simulations escape the overall trend. These are valley-spin degeneracies, occurring in these simulations because some valley splittings clash with the Zeeman splitting (Fig. 2.f ) at the input magnetic field of 1 T. While these degeneracies can be used for fast electrical driving Bourdet2018 ; Corna2018 ; gilbert_-demand_2023 , they significantly deviate from the target parameters for pure spin qubits. In practice, it is possible to either tune the valley splitting out of this regime or reduce the magnetic field to reduce the probability of accidental degeneracies, as discussed in the previous section.

We can also observe in Fig. 3c that the Dresselhaus parameter is bounded between two extreme values for each electric and magnetic field. This can be understood by analysing the perfectly flat [001] interface model, which introduces a distinction between the two sublattices in the diamond structure Ferdous2018 . Fig. 3e shows that in this case the Dresselhaus parameter is maximally positive for one sublattice termination and inverts for the other – the reason for this inversion can be understood viewing the [001] terminations in Fig. 3f. In comparison, a rough interface will contain terminations in both sublattices, and the value of will then lie between these two limits (see also Supplementary Fig. 8).

Strategies for qubit control need to be designed according to these results in order to tolerate the natural statistical dispersion in qubit frequencies introduced by the oxide interface. Individual addressability is a particular challenge. The most common strategy explored so far for addressing a specific spin qubit relies on exploiting this g-factor variability, and driving a variable microwave field in resonance with its Larmor resonance frequency in order to induce spin rotations Veldhorst2014 . However, the fact that the spin-orbit effect has a maximum natural spread results in frequency crowding at large qubit numbers Fig. 3g, making it hard to address a given qubit without impacting other qubits with similar frequencies.

Instead, a more scalable pathway relies on a global microwave field acting on all qubits simultaneously hansen2023entangling ; hansen_pulse_2021 . Qubits will be driven in resonance with the global field (forming a dressed qubit seedhouse_quantum_2021 ), thus requiring that all qubits have identical frequencies aligned with the resonator frequency. Individual addressability is then achieved electrically, by tuning the qubits in and out of resonance via Stark shift. However, in the case of a magnetic field along [110], the range of electric control of the g-factors is insufficient to tune them into the same frequency as can be seen in Fig. 3g . The variability in Larmor frequencies can be reduced by pointing the magnetic field along [100] (Fig. 3h) and by reducing the field magnitude to less than 100 mT zhao_single-spin_2019 . These modifications lead to a standard deviation of less than 200kHz, which is ideal for driving degenerate qubits with high fidelity (assuming a 2MHz Rabi frequency in Ref. hansen_pulse_2021 ). The Stark shift tunability also decreases, such that control strategies might need to cope with the inability to tune qubits completely out of resonance hansen_pulse_2021 .

The role of charge impurities in the presence of interface disorder Semiconductor devices are in general exposed to the presence of charge impurities in the oxide layer, originated from dangling bounds, Pb-centres, oxide vacancies, and other defects Müller_2019_traps_solids ; elsayed_low_2022 . Some of these are fixed charged traps in the oxide, while others fluctuate over time, which is the origin of 1/f noise in semiconductor devices. The most concerning charges from a variability perspective are charged traps. While two-level fluctuators are still important to understand qubit noise and decoherence, their absolute impact on the variability of qubit parameters occurs at a much smaller scale stuyck_real-time_2023 ; zhao_single-spin_2019 ; ModelingShehata2023 .

Previous works have modeled charged traps as negative electron charges directly at the Si/SiO2 interface martinez_variability_2022 . However, factors such as the positive correlation between the SiO2 thickness with charge mobility in Hall bar devices yagi_oxide_thickness_2008 ; Intel2019 , and measured large Dingle ratio elsayed_low_2022 are possible signs that these charges might be dominantly located closer to the metal-oxide interface in some cases.

We simulated a uniform charge distribution distributed across bulk SiO2 with density nm-1 Intel2019 (see Fig. 4a). Each trap is assumed to lead to a deformation of the potential of

| (1) |

where the trap at and . Here we investigate the impact of these charges on spin qubits in the presence of interface disorder (Fig. 1b).

In most cases in Fig. 4b there are no charges trapped inside the dot region, so the quantum dot wavefunction is similar to the simulations without charged impurities (see Fig. 2c). The shifts in the potential profile induce small displacements of the quantum dots below the rough Si/SiO2 interface. This leads to variations in valley spittings and g-factors with respect to initial simulations (Fig. 4c-d). An average increase in the valley splitting is observed, which is presumably due an overall enhancement of the lateral confinement of the dots in the presence of the negative traps. This increase is typically larger for quantum dots that already had a large valley splitting (See Supplementary Fig. 12) due to their higher susceptibility to electric fluctuations. The dispersion of the dots centers is slightly larger (see Fig. 4e-f), but still small in comparison with the quantum dot size.

Only when the charge is inside the dot region, the quantum dot wavefunction is significantly affected (see, for instance, dot 2 in Fig. 4b). While the g-factor of this dot remains within range (Fig. 4c-d), the valley splitting enhancement is larger than what it is expected for typical values (See Supplementary Fig. 12). The probability of this effect happening is 5.6% for this particular charge density, as estimated from a Poisson distribution Tong_2020_variabilityCharges . This situation could also affect large scale architectures. However, it is unclear whether a qubit exposed to this type of defect would necessarily be unusable – the comparison between open and closed symbols in Fig. 4c-d indicates that the presence of traps does not increase the statistical dispersion of one-qubit parameters significantly. We will show next that the impact of traps on the two-qubit exchange coupling is also manageable with voltage offsets.

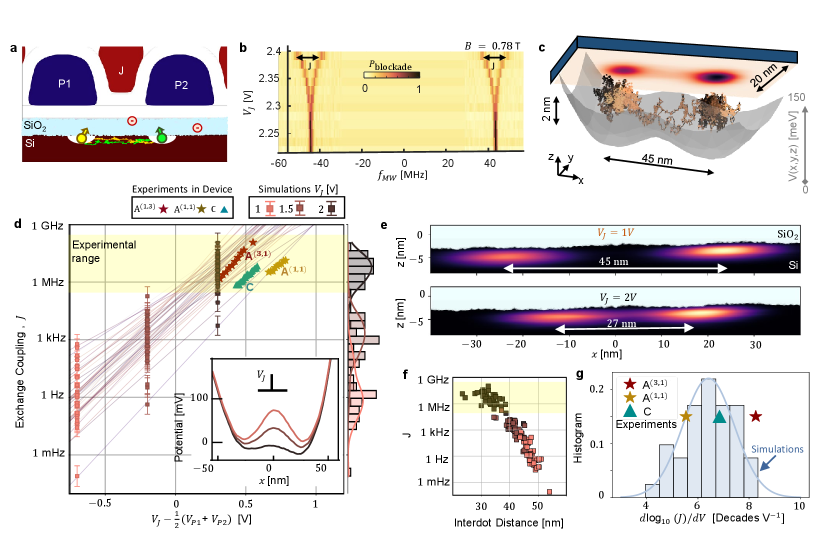

Variability of exchange interactions

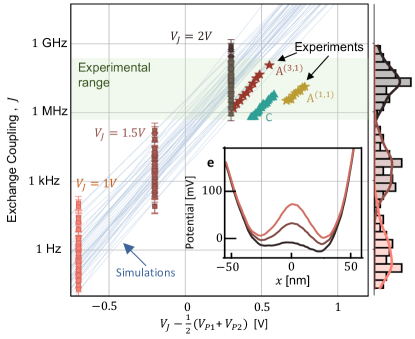

Besides the single qubit gate control, roughness and charge impurities also limit the homogeneity of the exchange coupling between neighbouring quantum dots. The differences in valley phase between dots, addressed in Fig. 2g, are the first source of variability in exchange coupling tariq_impact_2022 . In the worst case, the valley phases would be random and the resulting exchange coupling would be impacted by the destructive interference of the valley oscillations. The probability of a completely destructive interference is, however, negligibly small. The typical valley interference causes at worst an offset in the exchange coupling of one or two orders of magnitude, which is easily corrected by an offset in the exchange control gate voltage given that the tunability ranges from 6 to 10 decades per Volt. We find in simulations, however, that the disorder in quantum dot position has a stronger impact.

The fact that exchange coupling is a contact interaction means that any effect impacting how the wavefunction tails off from one dot into its neighbouring dot, such as interdot distance and potential barrier height, has an exponential impact Li2010 ; Saraiva2007 . In the devices investigated here, exchange is controlled by the action of the interstitial J gate (see Fig. 5.a). This gate induces a lateral displacement of the two dots toward each other reducing the interdot distance at a rate of approximately nm V-1 (see Supplementary Table 3). This is contrary to the picture frequently evoked in this scenario which assumes that the J gate controls the electron penetration length into the classically forbidden region between dots without affecting much its position.

In Fig. 5b we can see a method of extracting the exchange coupling by measuring the qubit resonant frequency for a randomly initialised pair of spins as a function of the J gate voltage.

To simulate this system, we use a path integral Monte Carlo approach Ceperley1995 . This method is relatively fast and intrinsically includes the effect of interactions in the electron dynamics. For each exchange simulation, we sample realizations of likely paths of two electrons in a three-dimensional double quantum dot potential obtained from a finite elements simulation (see Fig. 5c). Interface roughness can be readily included by defining a 3.1 eV step potential barrier to simulate the conduction band offset between silicon and the SiO2 layer. The paths of these electrons are allowed to exchange between the dots, and the impact on the path action is used to estimate the exchange coupling Pedersen2010 . The full method is described in Ref. CifuentesPIMC2023 and simulation details are included in the methods section.

In Fig. 5d we compare the J-gate tuning of the exchange coupling with random surface and trap realizations against the experimental data obtained from devices A and C. We plot the exchange against , which is an approximate measure of the voltage bias between the J-gate and the plunger gates (our dots are fully isolated from the reference voltage set by the reservoir). All devices were tuned to the symmetric operation point reed_reduced_2016 .

Our dataset combines qubits at the outer shell of quantum dots with one electron and 3 electrons. The exchange interaction is larger for higher electron numbers, due to the increasing overlap between the wavefunction of the quantum dots. This is observed in device A, where the exchange baseline of the (3,1) configuration is higher than in (1,1). These situations are so far not considered in the simulations, which are performed in the (1,1) electron configuration. The gate stack also has a significant role in the exchange control, affecting the effectiveness of the electric fields generated by the J gate in the channel. Here we compare devices A and C, which are both made with Pd/Ti gates with ALD oxides (see Table 1 and device architecture in Fig. 1f). Exchange control was also measured in devices E and F with Al gates in Ref. tanttu2023 , observing larger control rates and variability due to the absence of the ALD oxide and irregularities in the gate structure Saraiva2022 .

We found good agreement between exchange simulations and experimental data from devices A and C (Fig. 5d). An important part of this agreement was the inclusion of negative charged impurities in the model, together with interface roughness (see Fig. 4a). The charges that most significantly impact the exchange coupling between neighbouring dots are the ones located in the interdot channel CifuentesPIMC2023 . A single trap can reduce the exchange baseline a few decades. In total, this adds up to an average decrease of the exchange baseline of 1.5 decades in comparison with simulations without charge impurities, that have a higher baseline than experiments, as seen in Supplementary Fig. 10.

Importantly, the variability in exchange coupling can be compensated with more tunability. As seen in (Fig. 5e), the J-gate tunes the double dot potential inducing a displacement of both quantum dots to the centre by almost nm each. We can observe in Fig. 5f that this exchange dependence on displacement is consistent over multiple realizations, even when it is perturbed by the variability of the dot centres caused by surface disorder and charged traps. Because of the strong correlation between the inter-dot distance and the exchange coupling, we can associate the three orders of magnitude of exchange variability to these shifts in the interdot distance. Besides, the J-gate controls the interdot distance at an approximate rate of 10 nm per Volt, resulting in tunability ranges from 5 to 8 decades per volt in simulations and experiments (Fig. 5 g). This is large enough to compensate for the disorder and consistently hit a target “on” exchange rate, as indicated by the yellow region in Fig. 5d.

Discussion

The design of scalable quantum processor cells must be guided by a precise understanding of qubit variability. Besides demonstrating a complete strategy for diagnosing qubit variations for a given choice of qubit design, fabrication process and materials, this study leads to some general conclusions about the general physics of spins under Si/SiO2 interfaces. The main conclusion is that most of the qubit variability in current devices is explained by the roughness of the Si/SiO2 interface roughness. The presence of charge impurities is also significant in regard to two-qubit properties. Other effects (such as strain inhomogeneity and geometrical deformation of the gates) can be mitigated down to levels that are, at most, comparable with these intrinsic mechanisms.

Another conclusion is that electric tuning of qubit frequencies (using spin-orbit effect) and exchange coupling (using barrier gates) both rely to a large extent on moving the quantum dot laterally, dragging it against the rough interface. This may lead to considerations in future designs of quantum dots and the methods for characterising the interface .

Charge noise coming from two-level fluctuators (TLFs) can also couple to the qubits through a similar mechanism. The induced displacements of the dots in the rough interface lead to small g-factor variations that can affect important qubit metrics, such as the phase coherence stuyck_real-time_2023 ; Tanttu2019 . The charge noise couples directly to the qubit Stark shift, so the methods of this paper can be applied to investigate the microscopic nature of this effect cifuentes2023Crosstalk .

One remaining question is how much improvement can be realistically expected in the interface quality, and how it impacts the qubit performance. We address the last question in Supplementary Fig. 9, showing that the main benefits would be an enhancement of the average valley splitting and a smaller exchange variability. The spin-orbit coupling is not significantly affected due to its intrinsic atomistic dependence (Fig. 3f). Methods to improve the interface quality would involve replicating previously observed correlations between roughness amplitude and different fabrication parameters, such as growth time, oxide thickness, etc fang_evolution_1997 . The characterization methods developed in this study can help assess if the improvement in roughness amplitude occurs at the length scales that are more relevant for CMOS quantum processors.

This work focused on the case of Si/SiO2 interfaces, which has been studied enough that we are able to draw firm conclusions on its impact on qubits. Other oxides or dielectrics might also be understood adapting the methods developed here, providing pathways to shortcut the qualification of material stacks for quantum processor fabrication with the assistance of theoretical calculations.

Finally, this study realistically sets the ultimate variability of spin qubit parameters in CMOS devices. We may extract, for instance, the voltage offset that would be necessary to bring a qubit parameter to approximately the same value for all qubits in the architecture, which we call the voltage offset deviation for each parameter (see Methods section). For example, the typical voltage offset to bring valley splittings to the same range is 0.58 V, while doing the same for g-factors requires 0.23 V if the magnetic field is pointed towards [100] and 9.1 V for a field along [110]. The smallest value is for the exchange coupling variability which can be corrected with only 0.09 V voltage offsets. That clearly reveals that some parameters can be electrically tuned to a target system-wide value while others will require the implementation of strategies to circumvent the variability with a combination of locally generated control signals and robust global control strategies hansen_pulse_2021 . These results outline the minimum demands for a CMOS spin qubit architecture.

Methods

Fabrication process The SiO2 gate oxide (7.5-8.0 nm) was thermally grown on the silicon surface in a custom built high quality oxide furnace as part of a standard MOS device fabrication process. The gate fabrication process was iterated multiple times to improve yield, which was an enabling feature for this study, leading to the successful formation of several devices with nominally identical layouts.

Spin spectroscopy To measure the Stark shift and the difference in Zeeman splittings between the spins, we have to be able to measure the Larmor frequency of the two qubits at a given operation point. In these experiments we have double quantum dots which we use as two electron spin qubits. To begin, we initialise both electrons in the same dot forming a singlet state. We then separate the electrons and, depending on the rate of the separation, they will either end up in a state or having an odd parity, for instance an up-down state. To find the Larmor frequency we apply a fixed pulse or adiabatic microwave pulse with an antenna or resonator LauchtAdiabatic2014 . This pulse will flip a spin only if the applied frequency corresponds to the Larmor frequency. If the spin is flipped, the parity of the two spins will change too. We then bring the two electrons to a position where they are allowed to tunnel to the same dot only if their total parity is odd. If the parity is even, the electrons stay in their respective dots. We call this the Pauli-spin blockade-based parity readout Yang2020 ; Seedhouse2021PSB . The resulting charge state is read using a nearby charge sensor. Here we used a single electron transistor. The frequencies where we measured a flip in the parity of the two-spin states will correspond to the Zeeman splitting of one of the two qubits.

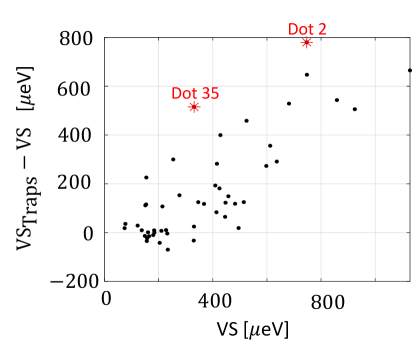

Measurements of valley splitting A tunnel rate-based spectroscopy method is used as an approximate measure of the valley splitting of quantum dots. The technique is as follows; 1) A repeated square-wave is applied to a dot gate, centred around a dot-to-reservoir charge transition. 2) The frequency of the square-wave is set equal to or faster than the dot-to-reservoir tunnel rate. In this mode, an electron will move in and out of the quantum dot in sync with the square wave, but for only a proportion of the square-wave repetitions due to the tunnel rate. 3) The amplitude of the square wave is swept from zero to 20 mV. The increase in amplitude causes excited state transitions to be accessed from the reservoir, which typically have increased tunnel rates to the quantum dot. 4) The changes in tunnel rate are fitted, and the splitting in amplitude between the ground state transition and excited state transition is multiplied by the dot gate lever-arm to retrieve the excited state energy. Here we assume the first excited state to be the valley excited state. This measurement technique is also explained in detail in yang2012 .

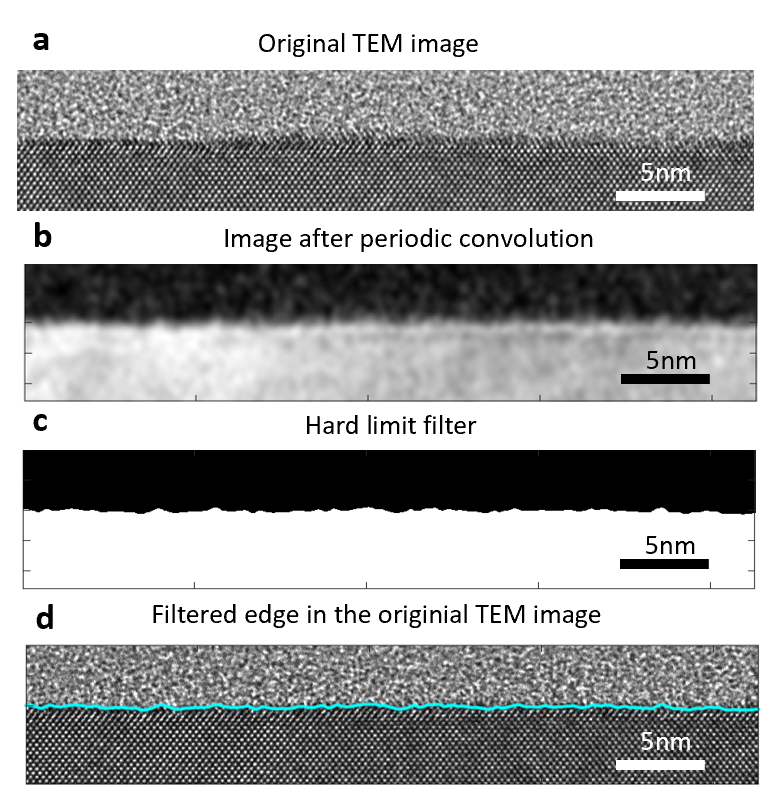

Image analysis to filter the Si/SiO2 interface from TEM images

In the TEM in Fig. 13a it is possible to discern the periodic pattern caused by the electron diffraction on the Si crystal. We apply a set of periodic convolutions to create a different background between Si and SiO2 regions. These convolutions are defined by four matrices with dimensions and entries

| (2) | ||||

| (3) | ||||

| (4) | ||||

| (5) |

where and . The result in Fig. 13b is obtained after taking the average of the images generated by four convolutions , where is the original image. Here the parameters and indicate the periodicity of the convolution in pixels in the and axis respectively. We define a parameter to be equal to , and . This parameter defines the lower bound scale at which the extracted power spectral density (PSD) of the Si/SiO2 interface is still not heavily affected by the convolution.

After the convolution, the lower part of the image corresponding to the silicon region should be darker than the upper side. Then we define a threshold parameter to segment both regions (Fig. 13c).We tune the parameters and until the fit clearly corresponds to the Si/SiO2 interface in the original TEM (Fig. 13d).

Si/SiO2 characterization of interface from TEM images We characterize the Si/SiO2 roughness from TEM images of devices T1 to T6 (see Supplementary Fig. 6) using a similar procedure to Goodnick1985 . To filter the interface, we apply image convolutions that enhance the differences between both materials. We then perform a power spectral density (PSD) decomposition of the filtered interface

| (6) |

and confirm that the scaling of the Si/SiO2 roughness is characteristic of a fractal self-affine interface Jacobs2017a ; Yoshinobu1995 .

We obtained an average Hurst exponent of and a roughness amplitude parameter of nm3 for our devices. The PSD profiles can change for TEMs taken at different regions of the same device. This is normal as some line versions of a 2D surface can be smoother than others, and this behaviour is observed even in a surface generated numerically. We found that comparing average 1D parameters from multiple TEM images accounts for a better estimate of the global 2D profile (Supplementary Fig. 6).

RMS characterization of Si/SiO2 interface from TEM images To compute the scaling of the RMS over a certain interface length characterised by the wavelength of its Fourier decomposition , we took separated segments of the fitted line surface from TEM image of width and computed the average RMS for each device. If a TEM has a width of 40 nm, we would compute the RMS for until reaching the atomic scale Yoshinobu1995 . We can select more subsegments when is small, which explains the smaller uncertainty of the average RMS for small . We found that the RMS scales with an exponent of as

| (7) |

which is expected for the PSD profile in equation (6) Jacobs2017a .

The RMS roughness amplitude of the computer generated surface was obtained by averaging the results over line segments of the 2D surface profile, as in Supplementary Fig. 6c with the power spectral density.

Random surface generation The computer model of the surface in Figure 1b was generated with a Fourier-filtering algorithm implemented in Matlab MonaMahboobKanafi2021 , that takes as input the 1D PSD profile in equation (6) and outputs a random rough surface with similar spectral density. The output surfaces look visually similar to the ones in the TEMs. To calibrate the model we compare the average 1D PSD and 1D RMS scaling profiles, with the edge profile in the TEM images until we find a good match (Supplementary Fig. 6).

Modeling of digital twin of the devices We create a 3D structure of the device in Matlab with the software provided by the DFX library. We begin by using a physical quantum dot electron-beam lithography (EBL) design layout as the primary framework and construct it as a 3D model that closely resembles its appearance in SEM and TEM images. Our software takes into account the levels of oxidation and thermal expansion that occur during the fabrication process to finely imitate the device geometry. We tweak these variables until the 3D model looks similar to transversal and in-parallel views of SEM and TEM images.

Electrostatic simulations and quantum dot model We import the digital twin device into COMSOL Multiphysics and perform electrostatic potential simulations with the integrated Poisson solver. We fit this to a harmonic model with a vertical electric field

| (8) |

where is the centre of the parabolic potential, is the electric field in the z-axis (typically to meV nm-1) and are the lateral curvatures (approximately 0.3 meV nm-2). We simulate potential sweeps from different gates to characterize their impact on the quantum dots (see Supplementary Fig. 7). The harmonic model allows to transform these actions to more intuitive parameters such as shifts in the electric confinement, dot movement, ellipticity, etc. A summary of this impact is included in Supplementary Table 3.

Atomistic simulations with interface roughness We perform tight binding simulations in NEMO3D in the 20-band model for Si, which intrinsically includes spin-orbit-interactions Klimeck2007 . In all simulations the magnetic field magnitude is set to T, and we only vary the magnetic field orientation. To include surface disorder, we terminate the silicon lattice with the local section of the rough surface in Figure 1b. We then label all the lattice sites above (below) the surface as SiO2 (Si), as observed in Figure 2a. The SiO2 region is modeled with a sp3 tight-binding (TB) model under a virtual crystal approximation (VCA). The SiO2 TB parameters are optimized to reproduce the electrical properties of the oxide, namely the bandgap of 8.9 eV, conduction band offset of 3.15 eV relative to silicon, and conduction effective mass of 0.44m0. The VCA model in TB assumes a well defined crystal structure, in this case zincblende with a lattice constant having the same value of Si, but treats each atom as a fictitious SiO2 atom. This is a standard way to model alloyed (SiGe) or disordered (SiO2) materials under the VCA in the atomistic TB technique. At the interface region whether an atom is marked as a Si atom or SiO2 atom then creates the atomistic disorder profile. The details of the model with parameter values can be found in kim_full_2011 ; Rahman_Roughness_engineered_valley_orbit .

By loading the surface roughness profile into NEMO3D, we are able to simulate quantum dot wavefunctions with atomic resolution under the correct local symmetries induced by the disordered surface. A limitation of the model is that we cannot simulate atomically disordered Si-O bonds in the oxide. Considering the various geometrical permutations of such bonds in an amorphous solid, it becomes a computationally challenging problem for large scale simulations. However, the VCA model does replicate the bulk electrical properties of SiO2. Despite this limitation, we are able to simulate effectively a Si-SiO2 interface that in general is hard to describe from a tight binding approach.

Valley Phase calculation with atomistic simulation The atomistic tight binding software outputs the electron densities of the two valley states ( and ) Saraiva2009 . Their difference may be interpreted in terms of an envelope function multiplied by cosine oscillations with the wavevector of the conduction band minima

| (9) | ||||

A colour plot of is shown in Fig. 2e. To compute the valley phase we average over the plane and perform a Fourier transform in the z-axis. There is a distinctive peak with frequency , as it is expected for valley oscillations. The valley phase is obtained from the complex phase of the transform at this frequency.

G matrix computation from atomistic tight-binding

Atomistic simulations with NEMO3D include intrinsically spin-orbit interactions in the 20-band model for silicon Klimeck2007 . For all simulations, we set the magnetic field magnitude amplitude to T and vary only the field orientation . The spin g-factor is independent of the magnitude of the magnetic field as long as the valley splitting is non-degenerate with the Zeeman splitting Bourdet2018 ; gilbert_-demand_2023 .

For any magnetic field , the spin part of the Hamiltonian of the system is

| (10) |

where is the -matrix and is the effective magnetic field after including spin-orbit effects. The atomistic tight binding software outputs the Zeeman splitting and also the full wavefunction of the ground state written in a base of atomic positions, orbitals and spins . From this we can estimate the mean spin vector . This spin aligns anti-parallel to the effective field by definition. In total, we have obtained the magnitude and orientation of the vector . If we perform this computation for three linearly independent magnetic fields , we will obtain the effective fields . Then, the linear system can be inverted to compute .

A typical G-matrix obtained from atomistic simulations is

| (11) |

where the basis is aligned with the lattice orientations . In here, is the bulk g-factor, as obtained from the asymptotic behavior of the simulations at low electric field. The entries and determine the in-plane spin-orbit-coupling and the parameters and describe the out of-plane components. The two remaining entries were calculated to be smaller than at all cases and hence approximated to . To obtain the g-factor at any magnetic field orientation we compute . If is an in-plane normal vector

| (12) | ||||

Then

| (13) | ||||

under the approximation which is valid in this case. After replacing and , we recover the expression that led to the variability distributions in Fig. 3.

Two electron Hamiltonian for path integral simulations

| (14) |

where each single electron hamiltonian is given by

| (15) | ||||

Here is the diagonal matrix denoting the effective mass of silicon electrons on each lattice orientation and is the velocity of each electron. is set to . is the double quantum dot potential simulated in Comsol as in Supplementary Fig. 7.

The oxide interface is defined by a smooth step of with the function Where nm is the silicon lattice parameter. defines coordinate of the rough surface at the position of projected in the xy-plane .

Path integral simulation of exchange coupling Hundreds of realizations of two-electron paths are sampled with path integral Monte Carlo (PIMC) with a Metropolis algorithm to minimize the partition function Ceperley1995 , where is the total action . We simulate both, paths that remain in separate quantum dots for the entire simulation and paths that exchange a few times between the quantum dots. The action of electron paths that exchange between the two dots is higher than for non-exchanging paths by an amount which allows to compute the exchange energy as Pedersen2010 . As the estimates of the operators are computed from average sampled path realizations, the method provides natural error bars determined by the standard deviation of . To adapt the method to 3D electrons in MOS quantum dots we had to do modifications to the main algorithm that are detailed in a separate paper (see Ref. CifuentesPIMC2023 ). For this simulations we used paths with time slices and ps. The path integral method converges at these values as shown in Ref. CifuentesPIMC2023 .

Voltage Offset Deviation (VOD)

| (16) |

For any parameter this metric estimates the deviation of voltage offsets that are needed to bring each variable to the average value . For the main parameters discussed in this paper we obtained:

-

1.

Valley Splitting: 0.58 V

-

2.

g-factor [110]: 9.1 V

Maximum among in-plane B-field angles -

3.

g-factor [110]: 0.23 V

Minimum among in-plane B-field angles -

4.

Valley Splitting: 0.09 V

The values of are obtained from roughness variability distributions. Only tunings in the range of hundreds of mV can be performed in real experiments. If the VOD is way higher than that, it means that it is not possible to tune to the same value for all qubits.

Estimating the tunability of qubit parameters To compute the tunability of each qubit we use simulations for different voltage tunings for the specific gates have a significant impact on each one of the variables. For the exchange () we focus on the J-gate. In contrast, single qubit parameters like g-factors and valley splittings can be tuned with more than one gate. In here we assume that the action is performed with a top gate and an additional lateral gate so that . At the same time, each of these tunings is divided as

| (17) |

Estimates for the impact of different gates on single quantum dot parameters can be found in Supplementary Table 3. The values for and where simulated from small changes in the simulation parameters as in Figs. 2f and 3 c-d.

Data Availability

The data for the figures generated in this study are provided in the Supplementary Information/Source Data file. Additional data and corresponding analysis code relevant to verify the results obtained here and generate the plots shown in this paper have been deposited in the Figshare database under accession code DOI: https://doi.org/10.6084/m9.figshare.23507439.

Code Availability

The path integral Monte Carlo algorithm to estimate exchange interactions with is described in Ref. CifuentesPIMC2023 . The algorithm to perform atomistic tight-binding simulations is described in Ref.Klimeck2007 . The original code used for processing and generating all the plots in this paper have been deposited in the Figshare database under accession code DOI: https://doi.org/10.6084/m9.figshare.23507439.

References

- (1) Maurand, R. et al. A CMOS silicon spin qubit. Nature Communications 7, 1–6 (2016).

- (2) Veldhorst, M., Eenink, H. G., Yang, C. H. & Dzurak, A. S. Silicon CMOS architecture for a spin-based quantum computer. Nature Communications 8, 1–8 (2017).

- (3) Philips, S. G. J. et al. Universal control of a six-qubit quantum processor in silicon. Nature 609, 919–924 (2022).

- (4) Veldhorst, M. et al. An addressable quantum dot qubit with fault-tolerant control-fidelity. Nature Nanotechnology 9, 981–985 (2014).

- (5) Noiri, A. et al. Fast universal quantum gate above the fault-tolerance threshold in silicon. Nature 601, 338–342 (2022).

- (6) Mills, A. R. et al. Two-qubit silicon quantum processor with operation fidelity exceeding 99%. Science Advances 8, eabn5130 (2022).

- (7) Yang, C. H. et al. Silicon qubit fidelities approaching incoherent noise limits via pulse engineering. Nature Electronics 2, 151–158 (2019).

- (8) Tanttu, T. et al. Consistency of high-fidelity two-qubit operations in silicon (2023). Preprint at https://arxiv.org/abs/2303.04090.

- (9) Zwerver, A. M. J. et al. Qubits made by advanced semiconductor manufacturing. Nature Electronics 5, 184–190 (2022).

- (10) Gidney, C. & Ekerå, M. How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits. Quantum 5, 433 (2021).

- (11) Beverland, M. E. et al. Assessing requirements to scale to practical quantum advantage (2022). Preprint at http://arxiv.org/abs/2211.07629.

- (12) Vandersypen, L. M. K. et al. Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent. npj Quantum Information 3, 34 (2017).

- (13) Hansen, I. et al. Pulse engineering of a global field for robust and universal quantum computation. Physical Review A 104, 062415 (2021).

- (14) Hansen, I. et al. Entangling gates on degenerate spin qubits dressed by a global field (2023). Preprint at https://arxiv.org/abs/2311.09567.

- (15) Gilbert, W. et al. On-demand electrical control of spin qubits. Nature Nanotechnology 1–6 (2023).

- (16) Vahapoglu, E. et al. Coherent control of electron spin qubits in silicon using a global field. npj Quantum Information 8, 1–6 (2022).

- (17) Hansen, I. et al. Implementation of an advanced dressing protocol for global qubit control in silicon. Applied Physics Reviews 9, 031409 (2022).

- (18) Stuyck, N. D. et al. Real-time feedback protocols for optimizing fault-tolerant two-qubit gate fidelities in a silicon spin system (2023). Preprint at http://arxiv.org/abs/2309.12541.

- (19) Vahapoglu, E. et al. Single-electron spin resonance in a nanoelectronic device using a global field. Science Advances 7 (2020).

- (20) Saraiva, A. et al. Materials for Silicon Quantum Dots and their Impact on Electron Spin Qubits. Advanced Functional Materials 32, 2105488 (2022).

- (21) Asenov, A. et al. Simulation of statistical variability in nano-CMOS transistors using drift-diffusion, Monte Carlo and non-equilibrium Green’s function techniques. Journal of Computational Electronics 8, 349–373 (2009).

- (22) Elsayed, A. et al. Low charge noise quantum dots with industrial CMOS manufacturing (2022). Preprint athttp://arxiv.org/abs/2212.06464.

- (23) Sabbagh, D. et al. Quantum transport properties of industrial . Phys. Rev. Appl. 12, 014013 (2019).

- (24) Lawrie, W. I. et al. Quantum dot arrays in silicon and germanium. Applied Physics Letters 116, 080501 (2020).

- (25) Burkard, G., Ladd, T. D., Pan, A., Nichol, J. M. & Petta, J. R. Semiconductor spin qubits. Rev. Mod. Phys. 95, 025003 (2023).

- (26) Müller, C., Cole, J. H. & Lisenfeld, J. Towards understanding two-level-systems in amorphous solids: insights from quantum circuits. Reports on Progress in Physics 82, 124501 (2019).

- (27) Jock, R. M. et al. A silicon metal-oxide-semiconductor electron spin-orbit qubit. Nature Communications 9, 1768 (2018).

- (28) Veldhorst, M. et al. Spin-orbit coupling and operation of multivalley spin qubits. Phys. Rev. B 92, 201401 (2015).

- (29) Tanttu, T. et al. Controlling Spin-Orbit Interactions in Silicon Quantum Dots Using Magnetic Field Direction. Physical Review X 9 (2019).

- (30) Ruskov, R., Veldhorst, M., Dzurak, A. S. & Tahan, C. Electron g -factor of valley states in realistic silicon quantum dots. Physical Review B 98, 245424 (2018).

- (31) Ferdous, R. et al. Interface-induced spin-orbit interaction in silicon quantum dots and prospects for scalability. Physical Review B 97, 241401 (2018).

- (32) Gamble, J. K. et al. Valley splitting of single-electron Si MOS quantum dots. Applied Physics Letters 109, 253101 (2016).

- (33) Martinez, B. & Niquet, Y.-M. Variability of Electron and Hole Spin Qubits Due to Interface Roughness and Charge Traps. Physical Review Applied 17, 024022 (2022).

- (34) Yoshinobu, T., Iwamoto, A., Sudoh, K. & Iwasaki, H. Scaling of Si/SiO2 interface roughness. Journal of Vacuum Science and Technology B: Microelectronics and Nanometer Structures 13, 1630–1634 (1995).

- (35) Goodnick, S. M. et al. Surface roughness at the Si(100)-SiO2 interface. Physical Review B 32, 8171–8186 (1985).

- (36) Jacobs, T. D., Junge, T. & Pastewka, L. Quantitative characterization of surface topography using spectral analysis. Surface Topography: Metrology and Properties 5 (2017).

- (37) Boter, J. M. et al. Spiderweb array: A sparse spin-qubit array. Phys. Rev. Appl. 18, 024053 (2022).

- (38) Ha, W. et al. A flexible design platform for si/sige exchange-only qubits with low disorder. Nano Letters 22, 1443–1448 (2022).

- (39) Ibberson, D. J. et al. Large dispersive interaction between a cmos double quantum dot and microwave photons. PRX Quantum 2, 020315 (2021).

- (40) Sigillito, A. J., Gullans, M. J., Edge, L. F., Borselli, M. & Petta, J. R. Coherent transfer of quantum information in a silicon double quantum dot using resonant SWAP gates. npj Quantum Information 5, 1–7 (2019).

- (41) Kim, S., Luisier, M., Paul, A., Boykin, T. B. & Klimeck, G. Full Three-Dimensional Quantum Transport Simulation of Atomistic Interface Roughness in Silicon Nanowire FETs. IEEE Transactions on Electron Devices 58, 1371–1380 (2011).

- (42) Bersch, E., Rangan, S., Bartynski, R. A., Garfunkel, E. & Vescovo, E. Band offsets of ultrathin high- oxide films with si. Phys. Rev. B 78, 085114 (2008).

- (43) Yang, C. H. et al. Spin-valley lifetimes in a silicon quantum dot with tunable valley splitting. Nature Communications 4, 1–8 (2013).

- (44) Leon, R. C. et al. Coherent spin control of s-, p-, d- and f-electrons in a silicon quantum dot. Nature Communications 11, 1–7 (2020).

- (45) Nagayama, S., Fowler, A. G., Horsman, D., Devitt, S. J. & Meter, R. V. Surface code error correction on a defective lattice. New Journal of Physics 19, 023050 (2017).

- (46) Tariq, B. & Hu, X. Impact of the valley orbit coupling on exchange gate for spin qubits in silicon. npj Quantum Information 8, 1–7 (2022).

- (47) Tagliaferri, M. L. et al. Impact of valley phase and splitting on readout of silicon spin qubits. Physical Review B 97, 245412 (2018).

- (48) Bourdet, L. & Niquet, Y. M. All-electrical manipulation of silicon spin qubits with tunable spin-valley mixing. Physical Review B 97 (2018).

- (49) Corna, A. et al. Electrically driven electron spin resonance mediated by spin–valley–orbit coupling in a silicon quantum dot. npj Quantum Information 4 (2018).

- (50) Seedhouse, A. E. et al. Quantum computation protocol for dressed spins in a global field. Physical Review B 104, 235411 (2021).

- (51) Zhao, R. et al. Single-spin qubits in isotopically enriched silicon at low magnetic field. Nature Communications 10, 5500 (2019).

- (52) Shehata, M. M. E. K. et al. Modeling semiconductor spin qubits and their charge noise environment for quantum gate fidelity estimation. Phys. Rev. B 108, 045305 (2023).

- (53) Yagi, A. & Kawaji, S. Oxide thickness effects on electron scatterings at a thermally grown Si‐SiO2 interface. Applied Physics Letters 33, 349–350 (2008).

- (54) Wu, T. & Guo, J. Variability and fidelity limits of silicon quantum gates due to random interface charge traps. IEEE Electron Device Letters 41, 1078–1081 (2020).

- (55) Cifuentes, J. D. et al. Path-integral simulation of exchange interactions in cmos spin qubits. Phys. Rev. B 108, 155413 (2023).

- (56) Li, Q., Cywinski, L., Culcer, D., Hu, X. & Das Sarma, S. Exchange coupling in silicon quantum dots: Theoretical considerations for quantum computation. Physical Review B - Condensed Matter and Materials Physics 81, 85313 (2010).

- (57) Saraiva, A. L., Calderón, M. J. & Koiller, B. Reliability of the Heitler-London approach for the exchange coupling between electrons in semiconductor nanostructures. Physical Review B - Condensed Matter and Materials Physics 76, 233302 (2007).

- (58) Ceperley, D. M. Path integrals in the theory of condensed helium. Reviews of Modern Physics 67, 279–355 (1995).

- (59) Pedersen, J. G., Zhang, L., Gilbert, M. J. & Shumway, J. A path integral study of the role of correlation in exchange coupling of spins in double quantum dots and optical lattices. Journal of Physics Condensed Matter 22 (2010).

- (60) Reed, M. et al. Reduced Sensitivity to Charge Noise in Semiconductor Spin Qubits via Symmetric Operation. Physical Review Letters 116, 110402 (2016).

- (61) Cifuentes, J. D. et al. Impact of electrostatic crosstalk on spin qubits in dense cmos quantum dot arrays (2023). Preprint at https://arxiv.org/abs/2309.01849.

- (62) Fang, S. J., Chen, W., Yamanaka, T. & Helms, C. R. The Evolution of (001) Si / SiO2 Interface Roughness during Thermal Oxidation. Journal of The Electrochemical Society 144, 2886 (1997).

- (63) Laucht, A. et al. High-fidelity adiabatic inversion of a 31p electron spin qubit in natural silicon. Applied Physics Letters 104, 092115 (2014). https://doi.org/10.1063/1.4867905.

- (64) Yang, C. H. et al. Operation of a silicon quantum processor unit cell above one kelvin. Nature 2020 580:7803 580, 350–354 (2020).

- (65) Seedhouse, A. E. et al. Pauli blockade in silicon quantum dots with spin-orbit control. PRX Quantum 2, 010303 (2021).

- (66) Yang, C. H. et al. Orbital and valley state spectra of a few-electron silicon quantum dot. Physical Review B 86, 115319 (2012).

- (67) Mona Mahboob Kanafi. Surface generator: artificial randomly rough surfaces, MATLAB Central (2021).

- (68) Klimeck, G. et al. Atomistic simulation of realistically sized nanodevices using NEMO 3-D - Part I: Models and benchmarks. IEEE Transactions on Electron Devices 54, 2079–2089 (2007).

- (69) Rahman, R. et al. Engineered valley-orbit splittings in quantum-confined nanostructures in silicon. Phys. Rev. B 83, 195323 (2011).

- (70) Saraiva, A. L., Calderón, M. J., Hu, X., Das Sarma, S. & Koiller, B. Physical mechanisms of interface-mediated intervalley coupling in Si. Physical Review B - Condensed Matter and Materials Physics 80, 81305 (2009).

Acknowledgments

We acknowledge support from the Australian Research Council (FL190100167 and CE170100012), the US Army Research Office (W911NF-23-1-0092), the US Air Force Office of Scientific Research (FA2386-22-1-4070), and the NSW Node of the Australian National Fabrication Facility. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Army Research Office, the US Air Force or the US government. The US Government is authorized to reproduce and distribute reprints for Government purposes notwith- standing any copyright notation herein. J.Y.H., S.S., M.K.F. and J.D.C. acknowledge support from the Sydney Quantum Academy. This project was undertaken with the assistance of resources and services from the National Computational Infrastructure (NCI), which is supported by the Australian Government and includes computations using the computational cluster Katana supported by Research Technology Services at UNSW Sydney.

Author Contributions

W.H.L. and F.E.H. fabricated the devices, with A.S.D.’s supervision, on isotopically enriched 28Si wafers supplied by K.M.I. (800 ppm), N.V.A., H.-J.P., and M.L.W.T. (50 ppm). T.T., W.G, J.H , E.V, R.C.C.L, S.S provided measurements of the qubit devices with supervision of C.H.Y., A.S., A.L and A.S.D. The data was gathered by J.D.C., who used it to estimate the CMOS variability in comparison with one qubit and two qubit simulations. J.D.C performed the one qubit simulations with atomistic tight binding in NEMO 3D with the supervision of R.R and A.S. For two qubit systems, J.D.C performed the exchange simulations with an in-house Path Integral Monte Carlo code developed by P.Y.M , F.S and J.D.C. with the supervision of A.S. D.O coded an initial framework for the fractal analysis of the Si/SiO2 interface that was later improved by J.D.C with the supervision of A.S. F.E.H took the TEM images of the devices. J.Y.H and D.D coded the software that designs the digital twin of the devices with the supervision of C.C.E. and A.S. These digital twins where imported for electrostatic simulations in COMSOL by J.D.C. and D.D. with the supervision of C.C.E. M.K.F provided theoretical support at all stages. J.D.C and A.S wrote the manuscript, with the input from all authors.

Declaration of competing interests

A.S.D. is the CEO and a director of Diraq. WTT, WG, EV, CCE, AL, CHY, WHL, FEH, AS, and ASD declare equity interest in Diraq Pty Ltd. Other authors declare no competing interests.

Supplementary information

| Device | Si29 Purity [ppm] | Oxide Thickness [nm] | TEM Range [nm] | # of TEMs |

|---|---|---|---|---|

| T1 | 800 | 8.0 | 400 | 2 |

| T2 | 800 | 8.0 | 40 | 8 |

| T3 | 800 | 8.0 | 500, 70 | 2, 3 |

| T4 | 50 | 7.5 | 250, 40 | 2, 4 |

| T5 | 800 | 8.0 | 250, 50 | 2, 4 |

| T6 | 800 | 8.0 | 700 | 3 |

| Gates | [nm V-1] | [eV nm-1V-1] | [nm V-1] | [eV nm-1V-1] |

|---|---|---|---|---|

| P1 | -6.74 | 13.42 | -2.95 | -2.11 |

| P2 | 4.95 | -0.68 | 5.5 | 14.75 |

| J1 | 6.88 | 0.46 | -3.57 | -0.22 |

| P3 | 0.04 | -0.02 | 0.13 | 0.06 |

| J2 | 0.02 | -0.01 | 0.13 | 0.06 |